SoC検証時間を短縮する各種ハードウエアの選択(2/3 ページ)

デジタルLSIの設計が複雑になるにつれ、検証作業の複雑化も進んでいる。設計できるゲートサイズと、限られた時間で検証できるゲートサイズの溝は広がるばかりだ。それはEDAベンダーの努力だけでは、とても埋められるものではない。

自作の道

システムの試作を一から行なうことは、今日、ある意味では簡単であるといえるし、ある意味では昔より難しいともいえる。今日のFPGAの容量とスピードをもってすれば、数100万ゲートのASICの試作も可能だ。近年、米Synplicity社や米Synopsys社のようなEDAベンダーは、ASICを分割して、分割ブロックごとにFPGAにプログラムできるようなツールを提供することで、試作の作業を軽減しようとしている。今日、ASICの試作ソフトが普及してきたことで高速試作ビジネスが活気を帯び、米Cadence Design Systems社や米Mentor Graphics社といった伝統あるエミュレータベンダーにすら対抗しうる手ごわい企業が出現している。特に既製の試作システムを販売するベンダーは、システムを構築するか購入するか迷っている設計者にまずこう質問するという。「自分達でシステムを試作するだけの十分な時間や、基板ボード/システム設計のスキルをもったスタッフ、それに予算を用意できますか?」

ASICの試作システムを販売する米The Dini Group社の社長を務めるMike Dini氏は、高速試作システムは一から構築するよりも買った方が断然安くつくと語る。10年前までASICとFPGAの設計コンサルタントだったDini氏は、検証ツールへの不満から試作ボードの製作を始めた。今では設計サービス事業から手を引き、ASIC試作という急成長事業に注力している。現在は複数のベンダーがこのような試作システムを販売している(表1)。「エミュレーション分野の競合企業は、我々が単にFPGAの束を売っているにすぎないと言っているが、特に気にしていない。なぜならそれはある意味正しいからだ。当社が進めているビジネスは、最も容量の大きいFPGAをいくつもボードに搭載して、デバッグして、一から作るよりも安くお客様に提供する、ということである」とDini氏は言う。試作は重要なことかもしれないが、プロジェクト終了後には捨てられてしまうようなアプリケーションに特化したボードを組み立てるのは無駄だというのが同氏の意見だ。特別な機能をもったドーターボードは自作して、FPGAの部分は高速プロトタイピングシステムのベンダーから購入することをDini氏は勧めている(別掲記事「購入の検討」を参照)。

Dini氏をはじめとする人々は、たとえSynplicityやSynopsysなどの自動パーティショニングソフトウエアを使用したとしても、4個以上のFPGAを必要とするシステムを自作しようとすればたちまち壁にぶつかると考えている。特にプリント基板の設計に詳しくなければ、EDAベンダーが何と言おうとその作業は非常に困難になるだろうという。「作るか買うか。試作はそのいずれかだ。1個のVirtex FPGAがあれば端子数700といった大きなパッケージでも大丈夫だが、それが2個、3個、あるいは16個にもなると、設計、構築、テストの困難度は増していく。たとえば、プリント基板のオートルータで700端子のFPGAを2個処理するのは無理があり、多くの手作業が必要となる。3個になるとASIC試作が複雑になってくる。2個ならまだしも、3個のFPGAを実装するのならば、配線層数やプリント基板内の接続への配慮も必要だ」とDini氏は言う。最近のFPGAは自動パーティショニングソフトウエアとの適合性もよく、高速試作システムのほとんどのベンダーが、自社のシステムをSynplicity社の「Certify」などに対応させていると彼は述べている。

最新のFPGAの特徴は、スピードやロジックではなくI/O構造にあるとDini氏は言う。シリアライザとデシリアライザで一対の差動信号を出力するため、1個のFPGAを別のFPGAに接続する場合には、10:1の多重化によって約350MHzで動作する差動信号線が必要となる。35MHzで動作する設計ならば、108対の信号線を10:1で多重化し、1800の信号を2個のFPGAで分割することができる。「この方法であれば、自作システムでは非常に厄介なパーティション作業がずっと楽になる」とDini氏は語る。ASIC試作を設計に取り入れるときの取り組みの一つとして、設計プロジェクトが始まる前に、ASIC開発者が試作を念頭に置いて設計することが挙げられる。ASIC内のブロックをパーティショニングに合わせて配置するのもいいだろう。ASIC設計者にこの方法を取らせるのは難しいことが多い。「一般にASIC設計者はピラミッドの頂点にいるが、検証と試作はピラミッドの一番下に位置づけられることが多い。それが望ましい姿かは別として」(Dini氏)。

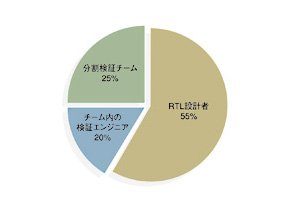

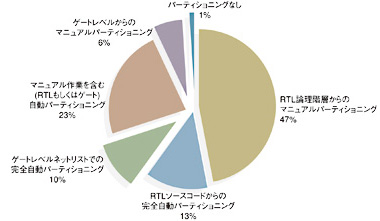

Synplicity社でASICツールのマーケティングディレクターを務めるJohn Gallagher氏は、ASIC設計の知識が豊富なほどパーティション作業は容易になると言う。Synplicity社が450人の設計者を対象に実施したアンケートでは、RTL設計者の55%がASICを試作システムにパーティショニングする作業を担当していると回答し、25%は独立した検証チームが試作を行うと回答している(図1、図2)。

購入の検討

Mike Dini

試作用のカスタムハードウエアを設計する場合、開発にかかるコストは条件次第で大きく違ってくる。設計に必要なデバイスの数もコストを決める大きな要因と言える。エンジニアリングチームが最初から正しい回路基板に行き着いたとしよう。プロトタイプの「製作」に関連する開発コストの範囲は、定義フェーズ(約2週間)、設計フェーズ(4〜6週間)、回路基板のレイアウト(4〜12週間)に及ぶ。設計者はこのほか、部品調達に2週間、組み立てに2週間、テストに4〜6週間を見ておかねばならない。これらすべてのフェーズを合わせると、全体で18〜30週間の期間を要する。さらに、回路基板の一般的なNRE(nonrecurring engineering)費として3000〜5000米ドル、マスク費約1000米ドル、小ロットの初期組み立て費2500米ドルを考慮に入れておく必要がある。

部品調達と一部のテスト機能は設計プロセスの過程で同時に検討できるが、試作の定義、回路図の作成、回路基板のレイアウト、組み立ては順番に行われなくてはならない。最初の組み立て品を入手してから2週間を必要とする場合は、自作品を動かせるまでに少なくとも16週間がかかることを意味する。エンジニアの単位料金が1時間100米ドルだとすると、6万4000米ドル分のエンジニアリング時間と最低5500米ドルのNRE費が必要だ。

上記の数字はベストケースのシナリオに基づいている。一般に試作品を設計する場合は、少なくとも4〜6カ月間の時間と10万米ドルのコストがかかる。3個以上の大規模FPGAを使用するならば、レイアウトだけで12週間近くかかる。BOM(部品)コストの大半はFPGAのコストによって決定される。また、LVDSやギガビット単位のシリアルインターフェースを必要とする場合は、設計に要する時間は劇的に増加する。

Copyright © ITmedia, Inc. All Rights Reserved.