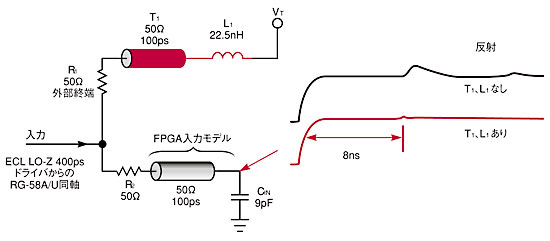

前回のコラムでは、受信回路の入力容量から終端抵抗に負荷がかかることで、終端の役割が妨げられる様子を示した。またこれに対し、アイソレーション用の抵抗R2を使って(図1)、受信回路の容量の影響を部分的に終端から切り離し、まずまずの結果を得た。ここでまず、T1とL1の部分は無視することにしよう。つまり、50Ωの外部終端抵抗が直接終端バイアス電圧VTに接続されていると仮定する。FPGA回路部のモデルは、BGAパッケージからチップ基板までの配線が少しと、チップ上の9pF容量を含む。ここで、アイソレーション用抵抗R2には基本的なトレードオフが存在する。つまり、抵抗値が小さすぎると、受信回路の容量CINから終端に負荷がかかり、大きな反射が生じる。逆にR2の値を大きくすると、反射は小さくなるが、信号の立ち上がり時間が劣化する。

今回は、見かけ上の終端インピーダンスを正確に50Ωにして、しかも受信信号の立ち上がり時間の劣化を最小限にする方法を示したいと思う。

実は、相反インピーダンスを使用することにより、これが可能となる。信号インピーダンスZ0が一定である場合、すべてのインピーダンスA(f)に対して、その相反インピーダンスはB(f)=Z02/A(f)で定義できる。例えば、50Ω回路では、9pFの容量と22.5nHのインダクタは、互いに相反インピーダンスになる。

AとBが相反インピーダンスであるとして、次の一般的な関係式が成立することを確かめてほしい。

この等式において、記号││は並列接続を意味する。この式は、簡単な計算で証明することができる。

この等式は、インピーダンスZ0+Aがあるとき、BがAと相反関係にあるインピーダンスZ0+Bをそれと並列に配置することで、インピーダンスを安定させられることを表している。その場合、最終的な並列回路のインピーダンスは、すべての周波数において正確にZ0となる。

図1では、入力信号は2つの並列なパスに分かれる。下方のパスには、Z0+Aのインピーダンスがある。Z0は50Ωの抵抗R2を表し、AはFPGA内の伝送線とコンデンサ回路を表す。

上方のパスのインピーダンスはZ0+Bである。Z0は50Ωの外部終端抵抗を表し、BはT1とL1の組み合わせを表す。

さてここが、今回のマジックのタネである。上方のパスのT1と下方のパスのBGA配線が同じ特性インピーダンスZ0を持ち、両方の線の遅延が同じで、L1=Z02CINであるとすると、インピーダンスAとBは必ず相反となる。つまり、上記の等式を適用する要件を満たしており、全体として終端インピーダンスが、すべての周波数において正確に50Ωとなることになる。

ここで使用するインダクタや設計上発生するビアによる2次的な寄生インピーダンスは、確かに回路の性能に影響を及ぼすが、1次効果としてはこの巧妙に補正された終端が完璧に機能する。

<筆者紹介>

Howard Johnson

Howard Johnson氏はSignal Consultingの学術博士。Oxford大学などで、デジタル・エンジニアを対象にしたテクニカル・ワークショップを頻繁に開催している。ご意見は次のアドレスまで。www.sigcon.comまたはhowie03@sigcon.com。

Copyright © ITmedia, Inc. All Rights Reserved.