チップ内ばらつきを考慮したLSI設計手法(3/3 ページ)

ここ数年のプロセス技術の進歩により、以前では考えられなかったような高集積度のチップ設計が可能になった。その一方で、製造工程で発生するさまざまなばらつきの問題が深刻化している。本稿では、チップ内ばらつきの影響を考慮した設計手法について解説する。

配線のばらつき

チップ内ばらつきの要因の1つに、配線の高さと線幅がある。これらにより、抵抗値と容量値の両方にばらつきが生じる。微細化が進むに連れ、配線による遅延の影響は大きくなる。そのため、配線のばらつきは正確にモデリングしなければならない。

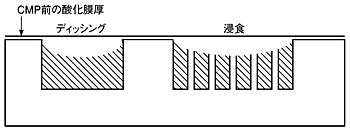

配線のばらつきは、CMP(chemical mechanical planarization)工程、リソグラフィ(露光)/エッチング工程における近接効果の影響により生じる。CMP工程におけるばらつきは、配線と絶縁体それぞれの材料の硬度が異なるために発生する。理想的には、配線層(銅配線と接続ビア)の下の絶縁層部にエッチングによってトレンチを形成した後、CMPプロセスによって配線とビアに必要な部分のみを残して不要な銅を除去することが望ましい。しかし、銅配線は絶縁層よりも柔らかいため、「ディッシング(へこみ)」と浸食が生じ、銅と絶縁体を均一に除去できない(図4)。ディッシングは線幅と密度の関数で表され、浸食は線面積と密度の関数で表される 。

CMPによる膜厚のばらつきはランダムに発生し、ウェーハ全体に影響する。このばらつきはチップごとにも発生し、大きなチップではチップ内ばらつきとなってしまう。このランダムに発生するばらつきを統計的にモデル化できれば理想的である。そのためのプロセスデータが得られれば、ウェーハ上の位置を変数に持つ関数としてモデル化することができる。このようにモデル化した場合、チップ上のX、Y座標値により、RC値に加算/減算する値が求められる。

上述したエッチングの近接効果は、「マイクロローディング」として現れる。これは、絶縁層で隔離された配線部分が、レイアウトパターンに依存して、ところどころオーバーエッチングされてしまう現象のことだ。デュアルダマシン構造では、単一のメタル蒸着ステップのみで主要な配線とビアのメタル部分を同時に形成する。つまり、トレンチとビアが同一の絶縁層上で形成される。オーバーエッチングが生じると、トレンチ部分が大きくなり、金属配線幅が大きくなってしまう。

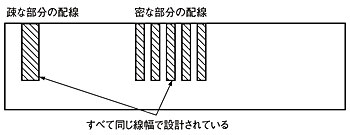

リソグラフィによる影響も問題となる。リソグラフィ工程において回折と局所的な散乱が生じると、配線が密集した部分で過度に露光したり、隔離された配線が露光不足になったりする可能性がある(図5)。

こうした影響は、タイリングやメタルスロッティングによって密度のばらつきを減らすことで緩和することが可能である。タイリングのアルゴリズムによって、得られる結果は異なるが、一般的に密度のばらつきが小さいほどチップ上の線幅のばらつきは小さくなる。

ただし、タイリングを実施することには欠点もある。タイリングでは、SoC設計フローの最終ステップの1つとして、密度に関するパラメータ抽出を行って計算を実行する。タイリングの前後では、計算によって得られた抵抗/容量値が異なる可能性がある。また、タイリングを行うと、新たに小さな遅延が生じる。つまり、タイリングを行った結果、最終的に目標とする動作周波数が実現されない可能性があるわけだ。目標が達成されるか否かは、タイリング要件を満たすために用いた手法に大きく依存する。

プロセスばらつきのモデリング

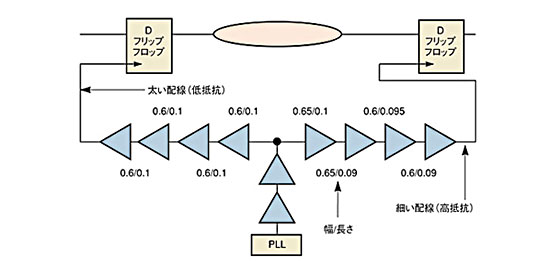

CMOSトランジスタの駆動電流を制御する主要なパラメータの1つは、ゲート長とゲート幅である。これらは、ランダムな影響とランダムでない影響を受けてばらつく(図6)。また、駆動電流は、閾値電圧とゲート酸化膜の膜厚にも大きく依存する。これらは、ランダムな影響のみを受ける。ランダムな影響は、イオン注入量、酸化膜の成長速度、ゲート酸化膜におけるストレスのばらつき、リソグラフィによる勾配、エッチングによる勾配などによって発生し、ロットごと、さらにはウェーハごとにばらつく。

トランジスタのミスマッチは、面積に比例する。各プロセスおよびライブラリには、スタンダードセル設計における標準チャンネル長がある。その値よりも大きいセルを選択することにより、ばらつきを抑えることが可能である。例えば、クロックツリーセルとしては駆動能力の大きいセルのみを使用し、ばらつきを最小化することで、サブツリー間のミスマッチを最小にする。このような具合に、大きさの異なるセルを適宜選択するわけだ。チップ上の有効チャンネル長と幅には大きなばらつきが生じることがある。このばらつきの大きさは、製造工場や使用するプロセスによってさまざまである。最悪の場合でも、ウェーハ全体にわたり、長さと幅のばらつきはプロセス上の許容値の半分程度である必要がある。

温度のばらつきも、タイミングに影響を及ぼす可能性がある。チップ内での消費電力分布が均一でない場合や、配線の発熱、チップやパッケージ材料の熱特性により、チップ上で動作温度のばらつきが発生することもあり得る。温度分布はIRドロップの分布とほぼ一致するが、回路/配線の密度やハードマクロの位置、その他の要因により少し異なる場合がある。

ディープサブミクロンプロセスにおけるタイミング解析はますます困難になってきた。プロセス、電圧、温度に変動があっても歩留りが確保できるようにするためには、設計者はこれまで以上に注意深くばらつきの影響を解析しなければならない。ばらつきはますます増大する傾向にあるが、それを現実に即したモデルとして表現する必要がある。そうしなければ、目標とする性能が達成できなかったり、歩留りが低下したり、チップが正常に動作しなかったりといったことが起こり得る。逆にいえば、歩留りの向上には、ばらつきのモデリングが必須である。

Copyright © ITmedia, Inc. All Rights Reserved.