新しいプロセスノードが出現するたびに、LSI設計はさらに困難になる。しかし、90nmや65nmプロセスノードへの移行については、これまでのように単に難易度が高まるだけではなく、従来とは根本的に何かが異なるのではないかと考える設計者が多い。90nmと130nmの設計手法で異なるとすればその違いは90nm特有のものなのか、それとも65nmではさらに違いが大きくなるのか。この疑問を解決するには、うまく設計を行った設計チームに話を聞くのが一番だろう。

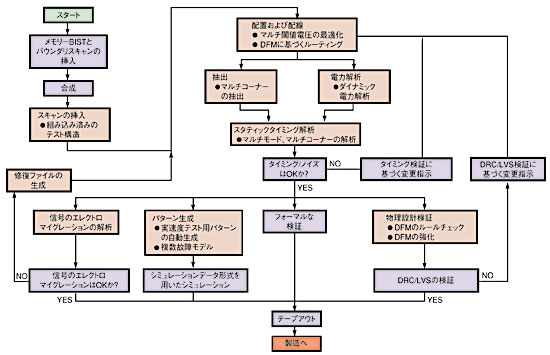

特にセルベースの設計を行うチームにとっては、90nmプロセスと65nmプロセスにはその複雑さの度合いに大きな違いがある。ファブレスASICベンダーである米Open Silicon社で使われている90nm用のトップレベルの設計フロー図には、新しい分岐が増えている (図1)。Open Silicon社のASIC設計マネジャーであるJay Jayaprakash氏によると、90nmプロセスノードにおける新しい課題は、電力、シグナルインテグリティ、DFM(design for manufacturing:製造容易化設計)、DFT(design for testing:テスト容易化設計)に分けられるという。

図1 OpenSilicon社で使われている90nm用のトップレベルの設計フロー図 OpenSilicon社では、90nmプロセスでの量産の実現を保証するために、設計フローにおいてかなりの数の段階(影付き部分)を追加または修正している。※クリックすると拡大表示します。

電力とシグナルインテグリティに関しては、より複雑さが増しただけと考えてよい。確かに90nmプロセスノードでは電力管理はさらに重要な問題となり、セル設計者、ツール設計者、ロジック設計者が共同で対処する必要がある。しかし、この問題は130nmプロセスノードの場合と基本的には変わらない。微細化が進むほどリーク電流は大きくなり、問題はさらに困難になる。同様に、シグナルインテグリティ解析も微細化が進むほど難しくなる。さまざまなツールを使って、その結果を注意深く解析する必要がある。

90nm設計フローの課題

Jayaprakash氏は、90nmプロセスノードのデジタル回路設計フローにおいてはSPICEがさらに中心的な役割を担うという。クロックネットに対してSPICEを利用するのは、数世代前から行われているが、クリティカルな信号パスに対しても詳細な解析が重要になってきている。信号パスに対しては、デジタルタイミング解析に関連する新しい技術の必要性を感じる。「STA(スタティックタイミング解析)では管理しきれなくなってきている」とJayaprakash氏は指摘する。「ツールの操作モードごとに異なるプロセスコーナーがあり、STAの基本データを提供する寄生素子抽出ツールにもさまざまなコーナーがある。すべてのコーナーを考慮しようとすると解析を50〜60回も実行しなければならず、それによって得られた膨大なデータをどう扱えばよいのか分からなくなってしまう」(同氏)。

STAがますます複雑になるに連れ、米IBM社のSSTA(統計的STA)ツールが注目されるようになってきた。プロセスと抽出したデータの組み合わせごとに単一のSTAを実行する代わりに、SSTAでは各遅延を確率分布として表し、ネット上を流れ、出力へとつながるこの分布に対して処理を行う。出力自体も統計的な分布として表現される。このツールに関して設計チームからは、賛成意見よりも懐疑的な意見が多い。その理由の1つは、正確な遅延分布を得るためには、膨大な量のプロセスに関するデータが必要となるが、それはどうするのかという点に疑問があることだ。SSTAツールはプロセスモデルと密接に関連するため、IDM(integrated device manufacturer:垂直統合型半導体メーカー)や製造工場を持つASICメーカーでのみ実用可能なのかもしれない。もう1つ、多くの設計者を悩ますさらに大きな問題がある。それは、ツールにより得た結果をどうすればよいのかという問題だ。例えばネットのタイミングスラックが−12psを中心に24psの標準偏差で統計的に分布していることが分かった場合、どうすればよいのか。「ツールはあるが使い道が分からない」と米Qualcomm社の主席エンジニアであるRiko Radojcic氏は指摘する。「SSTAはファジーな世界で、白黒が明確ではない」。

設計チームが90nmプロセスへと移行する際に直面する、従来との最も根本的な違いが何なのかという問いに対する答えが、統計的タイミングに関するこの疑問からぼんやりとではあるが見えてくる。タイミング解析にかかわるエンジニアがネットの遅延はどのくらいか、とプロセスエンジニアに尋ねたとしよう。プロセスエンジニアは、遅延はトランジスタのスイッチング速度に依存すると答えるだろう。その速度は、トランジスタの閾(しきい)値電圧、ゲートリーク電流、有効チャンネル幅と長さ、ドレイン抵抗、ソースおよびドレインの接触抵抗に依存する。これらの値は、ソースとドレインのインプラントおよびゲートポリシリコンのサイズや形状によって変動する。また、90nmプロセスでは大きくばらつきが生じるソースやドレイン接点の形状や構造にも依存する。さらに、トランジスタのウェルインプラントの近接度、ポリシリコンゲートのパターンの密度やピッチ、ポリシリコンにおけるコーナー間の距離や幅の変化に依存する。

以上のような点やその他多くの要因により、タイミングクロージャを達成することが自分の責任範囲だと思っていたエンジニアは突然、それまでに経験したことのないプロセス変数の問題も解決しなければならない。

FPGA、メモリー、CPUのベンダーなど、プロセスノードの先駆者であり最新のプロセスを最初に採用する設計チームには、上述のような恐ろしい展開が待ち受けている。これらすべての変数にどう対処するのかという問題が、実際に設計チームにのしかかってくるのだ。これを解決するには、社内の製造工場やファウンドリなどのプロセスプロバイダとの連携を密にする必要がある。そして独自のセル設計、モデリング、プロセスエンジニアリングのグループも集まり、ファブプロセスのエンジニアから提供されるデータを活用しなければならない。

しかし、このような体制は、通常のセルベース設計チームには不向きであるし、ASIC設計チームに適用するのは不可能である。大規模なファウンドリが一般のファブレス企業に対して基本的なデータを提供しているとはいえ、

プロセスに関してこれほどまでの深い知識を持つ必要があるとすれば、コストがかかり実用的ではない。業界ではこの窮境から脱するためにいくつかの手法を採用している。最初は、130nmプロセスで使われた最も簡単な手法が90nm設計でも使われていた。この時代に推奨された設計ルールでは、ファウンドリのプロセスエンジニアが規則を定めることにより、クリティカルなパラメータに大きなばらつきをもたらす要素を、設計チームが物理設計(マスク設計)に加えることを防止できるとしていた。その上で、チップの仕様や、より高い抽象レベルの設計では、ファウンドリが提供し始めたセルライブラリにガードバンド(ばらつきを考慮した設計マージン)を設けることで、ルールにさえ従えばチップ設計者は予期せぬ問題に直面することはないと、プロセスエンジニアが保証できたのである。

しかし、この手法を90nmプロセスノードに適用すると、予期せぬ問題が発生した。ファウンドリのエンジニアは新しい設計ごとに新たな問題を検出し、それらを防ぐための規則を新たに作成し続けることになったのである。このため、90nmプロセスの先駆者に限らず、初期のユーザーは、次々に変化する規則に対応しなければならなかった。1つだけだったルールのリストはすぐに2つに増えた。つまり、強制ルールと推奨ルールである。さらにガイドラインが追加された。現在では、設計チームは3つの問題を抱えている。1つ目の問題は、ルールが多すぎてそれらに従っているかどうかをチェックするだけでも非実用的だという点である。2つ目は、それらのルールにある程度従うと、性能や集積度の面で90nmプロセスに移行する利点が得られなくなることだ。3つ目は、ルールに従うと、LSIにとって重要な物理的な構造が実現できなくなってしまう点である。

これらの問題は65nmプロセスでは一層悪化する、と米NEC Electronics America社バイスプレジデント兼ゼネラルマネジャーのKazu Yamada氏は指摘する。「チェックするルールが増え続けるだけの問題ではない。65nmにおいては、ルールを追加することが問題の解決にはつながらない。その制約すべてに従っていたのでは、チップを設計することができない」(同氏)というのだ。それでは、ルールを定めることに何の意味があるのだろうか。設計者に単にルールに従うように指示するだけのレベルと、その設計がそのプロセスではどのような結果をもたらすのかを設計者に理解してもらうレベルの間の中間的な段階が必要なのである。簡単に言えば、ルールを定めるのは、設計者が利用可能なモデルを作成するためだ。理論的には、ネット上のタイミングに変動をもたらすばらつきの要因をすべて特定することができる。これらの要因を、統計的に、または物理的にモデル化する。このモデルを用いて、どのような選択をするとどのような結果が得られるかを設計者に示すことができる。モデルによって、設計者が実際に使えるデータが提供できれば理想的だ。そのデータとは、正確な寄生容量、遅延、電流などの値である。

モデルを配置配線ツールや合成ツール、フロアプランナーに取り込むことで、完全にプロセスを考慮した設計フローが作成できればより望ましい。ばらつきにつながるすべての問題に対してツールが対処してくれれば、設計者は、ツールや開発ステップはいくらか増えるかもしれないが、130nmプロセスの場合と同様の作業を行えばよいことになる。しかし残念ながら、そのような設計フローは実現されていない。問題の1つは、ばらつきの原因となるリソグラフィ、CMP(chemical mechanical polishing)といったプロセスステップをモデル化することがそもそも難しいという点である。装置ベンダーやプロセスエンジニアは、PCM(process compact models)を採用しているが、PCMは「コンパクト」という名称にもかかわらず複雑だ。これらのモデルはチップ設計や多くのセル設計において速度が遅すぎる。しかも、製造装置やファウンドリの世界でしか使われない入力を多く必要とする。例えば、CMPのモデルでは、パッド組成、時間に対するパッド圧力、バックプレート構造、スラリー組成、スラリーをウェーハに供給する位置と時間、回転速度、温度、電界強度などの入力が必要になる。しかもCMPはモデルのたった1段階にすぎない。

以上のことからEDAメーカーも、おそらくしぶしぶではあるが、ファウンドリや装置ベンダーと共同でPCMからデータを抽出し、より簡単で迅速な実行が可能なモデルに改良し、チップの設計段階で制御可能な入力のみで済むように変更を行っている。「PCMから開始して、設計者が必要な部分のみを抽象化することが必要である」と、米Synopsys社でDFM担当バイスプレジデントを務めるAnantha Sethuraman氏は述べている。個々のプロセスに対応する抽象化されたモデルを作成し、目まぐるしく変化する状況に応じてそれを変更していかなければならない。同氏は「ファウンドリがわれわれと共同で抽象モデルを更新していき、われわれはその変更版を顧客に提供している。90nmでは現在、業界内でこのようなプロセスが統一されつつあり、徐々に安定してきている」と語る。

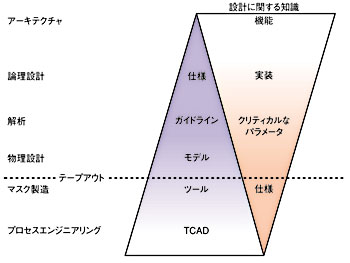

図2 適応型抽象化プロセス チップ設計においてもプロセスに関する知識が必要になってきているが、設計の上流ではそれが抽象化されている必要がある。逆に下流のプロセスエンジニアリングでは、設計に関する知識が必要になってきている。

米Cadence社のナノメーター解析および検証グループのグループディレクタを務めるDavid Thon氏は、上述したプロセスを「適応型抽象化」と呼んでいる。同氏は、設計チームとファウンドリ間で受け渡しされる2方向の情報の流れを示している (図2)。ファウンドリからの情報は、上流のチップ設計工程の初期段階へと流れるため、より抽象化されることが必要となる。セル設計者は、ネットにおける速度とばらつきのトレードオフに関心があり、開発者は歩留りを向上させるための構造や制約に関する抽象的な情報のみを知りたいと思っているだろう。一方、OPC(optical proximity correction) ツールを用いるマスク製造者は、回路におけるポリゴンの集合の役割について正しく理解したいと思っているかもしれない。プロセスエンジニアは、性能と歩留りに関連する部分のみを必要としているだろう。

現時点では、これらのモデルもPCMも、ネットの電気的特性を正確に予測したり、選択した設計がチップの歩留りに与える影響を正確に定量的に示したりすることはできない。「設計者に対して、ある程度の安全性を保証することができる。その変更を加えることによってどのような影響が生じるか、どういうときにチップに不具合が生じるのか、という疑問に対してある程度の情報を提供することが可能だ」とSethuraman氏は述べる。

プロセスのばらつき

EDA業界のアプローチにおけるもう1つの限界は、現在のところ、エンジニアがよく理解しているばらつきを持つプロセスステップの抽象モデルしか構築されていないという点である。実際にモデルが構築されているのは、リソグラフィとCMPの2つだ。リソグラフィには、エッチングプロセスのモデルの一部が含まれる場合もある。業界では、ウェーハ処理中に生じた電気的なパラメータの変動につながるその他すべての要因を、「ばらつき」としてひとまとめにしている。「高度なプロセスには2000から3000のばらつき要因がある」と、NEC Electronics America社のYamada氏は言う。「すべてのばらつき要因をモデル化してEDAツールに取り込むのは不可能だし、EDAメーカーが独自のプロセスモデルを作成することもできない。EDAメーカーにできることは、ますます増加していくプロセスコーナーに対処できる高速なツールを提供することだけだが、EDAメーカーとしてもこれ以上コーナーを次々と追加していくわけにはいかない」(同氏)。

歩留りを考慮した最新のツールを使っても、設計チームがプロセスの詳細を理解せずに済むわけではないことが分かっている。せめてセル設計者やカスタム回路の設計者のみがこの問題にかかわればよいのではないかという期待が持たれているが、残念ながらその通りにはならないだろう。

Yamada氏は、「90nmにおいてガードバンドのみで対処しようとした。その結果、チップはサイズが大きすぎるか、または速度が遅くなってしまった」と語る。そこでNEC Electronics America社は、セルライブラリにばらつきの問題を深く取り入れることにより、歩留りの高いセルにするか、性能の高いセルにするかを物理設計者が選択できるようにしている。物理設計を行うチームには、自らのリスクを査定し、元の設計の意図を理解して、選択を行うことが要求される。

この方法では、ASICユーザーとCOT (customer owned tooling) ユーザーが明確に区別される。「ASICユーザーはわれわれに設計を任せて、DFMの問題を解決してほしいと思うだけだ」と、Yamada氏はいう。「COTユーザーは、サイズ、性能、消費電力に対する要求が高く、設計におけるクリティカルな部分の1つ1つに対して、仕様と歩留りのトレードオフに直接かかわりたいと思っている。そのためにはこれらの問題を深く理解する必要がある。COTユーザーは、この作業にかかわった経験を持つことが望ましい」(同氏)。

NEC Electronics America社の経験によると、設計に対する要求が高いほど、設計チームに要求されるプロセスに関する専門知識のレベルも高くなる。90nmプロセスを使用する目的が、チップを小さくすることと、動作時のダイナミックな消費電力を低減することだけならば、RTL (register transfer level)ロジックに適切なタイミングファイルとテストケースを添えて、後はASICベンダーに任せればよい。しかしチップを小型化し、高速にして、消費電力を低減するには、より積極的に回路設計を行うことによってどれだけのリスクを負うことになるのかをチップ設計者がしっかりと把握しておく必要がある。

例えば、Radojcic氏によると、Qualcomm社では90nmプロセスに対してほぼ純粋にセルベースの設計フローを使用している。物理設計者に提示されたDFMガイドラインは多く存在したが、DRC (design rule checking) を実施するのと同じ方法でDFM問題に対処していた。つまり、レイアウト後にDFMに対応した検証を実行するのである。同社は独自のセルライブラリを開発しており、設計済みのセルに対してはファウンドリが検証ツールを実行して、変更すべき点を提案する。しかし、その内容や意味を理解しているのはセル設計者のみであった。「ファウンドリは、設計チームがリソグラフィやCMPの知識を持つ必要はないと考えていた」と、Radojcic氏はいう。

65nmプロセスでの大きな変更点は、ファウンドリがDFMスコア算出ツール群を、自身で実行するようにとQualcomm社に提供したことである。同社では主にこれらのツールを、フルカスタムブロックの場合を除き、個々のセル設計に使っていた。設計チームは、ツールによるブロックの検証で一定以上のスコアが達成される必要はないとしていた。実際、設計者はテープアウトした後で時間の余裕があるときにツールを実行したりしていた。「ツールを使用して歩留りの問題を特定したわけでもなければ、一部で予測されているような“限界”を検出したわけでもない。われわれは65nm設計でもある程度の歩留りを達成している」とRadojcic氏はいう。

ばらつきの問題に対しては、Qualcomm社では従来のコーナーケース解析を使用している。「細部が見えすぎると、マージンをとりすぎてしまう可能性がある」とRadojcic氏はいう。しかし、設計でマージンをとりすぎてしまうのは、まだ存在もしないプロセスのモデルや解析ツールのせいではなく、熟練した設計者の技術と経験に依存することによる、避けられない代償かもしれない。「設計を選択し、DFMを目的として加えた変更と、それが歩留りに及ぼす影響を関連付ける方法がない」と同氏は指摘する。「ある意味、設計チームの経験から得られたもの以外には、これらすべてのツールへの投資によって目に見えるものは得られていない。現在われわれは65nm用の設計フローを用いて、45nmにおいてDFMをよりフォーマルなものにするための評価を行っているところだ」(同氏)。 この問題については、SSTAを採用し、その使用方法を習得するべきか、あるいは、できる限り多くのばらつきを取り入れてそれらをモデル内に正確に反映させるべきかという2つの方法の間で迷っているという。

設計者が問題に直面した場合、それを解決する何らかの方法が存在するはずである。この場合の「何らかの方法」とは、その1つの問題個所の手直しのために新たにレイアウトし直すということではない。そのようなことをすれば、また別の個所にほかの問題が生じてしまうだろう。従って、Cadence社のようなEDAベンダーは、レイアウトの一部分を調整したり、リソグラフィ、CMPに対応したDFM検証やDRCの結果を反映したレイアウトを再検証したり、抽出ファイルに変更を追加したりすることが可能なツールを開発している。Cadence社は、この手法においてツールがデータベース全体をたどることなく、対象とする機能の周辺のオブジェクトを特定できるようにするには、設計データベースの基盤構造に変更を加える必要があると考えている。

設計者に求められるプロセス知識

ある設計が成功するかどうかは、バベルの塔のようにどんどんチェック項目が積み上がっていくコンプライアンスチェッカ、ルールチェッカ、解析ツールからのデータを取り入れつつ、自分自身の経験に基づいて設計を決定する熟練した設計者の能力にかかっている。台湾TSMC (Taiwan Semiconductor Manufacturing Company) 社では、この設計者の負担を軽減するための独自の方法を模索している。同社は65nmリファレンスフローにおいて、フローにかかわる8つのDFMパートナーに対して共通のデータ形式を作成/提供した。この形式を使って、クリティカル領域解析、リソグラフィ工程のチェック、仮想的なCMPモデリングを行う。「歩留りを予測するところまでは実現できない」と、TSMC社プロダクト・マーケティング部門設計サービスシニアディレクタのEdward Wan氏は述べる。しかし、「リソグラフィとCMPにかかわる設計上のホットスポットを予測することはできる。ツールの感度をばらつきデータに合わせることにより、歩留りを低下させる部分にはツールがフラグを立てる。この手法により、問題に対する修正作業をバックエンドのチップ設計者の守備範囲内に収めることができる」とも同氏は語る。

それでも、設計に対する要求が高いほど、設計者に知識が必要となることに変わりはない。米Altera社の設計エンジニアリング部門バイスプレジデントを務めるBradley Howe氏は、モデルやツールで設計者を支援できる範囲は小さいと見ている。Howe氏は、セルベースのフローを新規に採用する設計チームには同社の経験を知ってもらうべきだと考える。「少なくとも65nmに対しては、セルライブラリだけで問題を解決することはできないだろう」と同氏は指摘する。「プロセスばらつきに関する知識をライブラリやEDAツールに組み込むだけでは、ガードバンドを大きく設ける設計しか実現できない。ある種の設計ではそれでよいのかもしれないが、それではだめな場合もあるだろう。確かにわれわれが提供するのはフルカスタムフローである。しかし、われわれの経験からいえるのは、DFMの影響の及ぶ範囲をある抽象レベルまでに抑えることはできないということだ。その影響は最上位のアーキテクチャレベルにまで及んでいる。例えば、65nm向けにルーティング・アーキテクチャを開発していたときには、トランジスタのばらつきをいかに吸収するかという問題にどっぷりはまってしまった。開発に携わる者すべてがプロセスに関するある程度の知識を持つことが求められる」(同氏)。

Howe氏が最後に述べた考え方が、90nmや65nmプロセスノードの設計チームが直面する根本的な変化であるようだ。プロセスを最大限に活用するには、経験、ばらつきの要因に対する知識、その対処法、電気的特性に対する影響に基づいて、回路ごとにリスクを算出できる人材が必要である(別掲記事「グローバルな問題をも生み出すDFM」を参照)。

Howe氏は「90nmプロセスの採用を検討している設計チームへは、『何も待つことはない、今すぐ始めなさい』と助言したい」とした上で、「必要な専門家を雇うか、社内の人間を教育することだ。いずれツールやサードパーティでは問題に対処できなくなるので、そのためのインフラストラクチャをチーム内で構築する必要がある」ことを強調した。

グローバルな問題をも生み出すDFM

グローバルエンジニアリングでは、タスク管理に国境はないと考える。アナログ回路設計やカスタム回路設計のタスクは例外かもしれないが、世界各地においてブロック単位でデジタル回路設計を行う場合、どのブロックをどこのチームに割り当てても、得られる結果はほぼ同じである。つまり、デジタル回路設計に文化の違いは影響しない。

しかし、DFMという新しい世界では状況が異なる、と経験豊かな設計マネジャーは口をそろえる。その理由は、90nmプロセスとそれ以前のプロセスにおける設計上の1つの相違点にあるようだ。つまり、判断基準の違いである。

90nmプロセスノード以前は、メーカーが使う設計ルールでは、長い複数の配線を互いの近くに配置してはいけないなど、歩留りに影響を与える処理は禁じられていた。これらのルールに違反するとDRCツールがフラグを立て、誰かに修正されてしまうのである。

しかし、90nmプロセスでは、歩留りの低下を防ぐためのこれらの多くのルールが、ガイドラインに降格した。「現在では推奨ルールが多すぎて、それらすべてに従っていたのでは設計を行うことができない」と、NEC Electronics America社のKazu Yamada氏は述べる。一方で、これらのルールをすべて無視していたのでは、チップの歩留りは2桁にも達しないであろう。ブロック設計において、推奨ルールそれぞれが歩留りにどの程度の影響を及ぼすかを教えてくれるような魔法のツールは存在しないのである。

このため、90nmや65nmプロセスノードにおけるクリティカルなブロックの設計は、もはや設計者の判断に委ねられている。そして各設計者がとるアプローチはそれぞれの文化に基づいているようだ。

「日本人の場合、本質的にリスクは罪悪であるという考えで育っている」とYamada氏は言う。「米国の子供はリスクを負ったことに対して表彰されたりする。その文化がエンジニアの行動にも現れているのが分かる。日本の設計チームは、ガイドラインをうまく取り入れて注意を要する部分を特定することが得意だ。米国の設計チームはリスクを適度に無視しつつ、ある程度の結果を得る方法を探るのがうまい。65nmでは歩留りの問題にとらわれすぎていると設計を完成することができない。日米両方の文化的な姿勢を取り入れることが必要である」(同氏)。

Qualcomm社のRiko Radojcic氏も同様の見解を示す。「当社のデザインセンターは米国、インド、その他の国々にあるが、設計ガイドラインにあまり従いたがらないデザインセンターもあれば、従いすぎるデザインセンターもある」と同氏はいう。ただしRadojcic氏は、これをすべて文化の違いによるものとは見ていない。同氏によると、積極的なチームには、多くの場合専門知識を有する内部グループがいて、ファウンドリのガイドラインを、設計者が設計データに適用するための“フィルタに変換”しているという。専門知識を持つグループが存在しないデザインセンターでは、65nm設計のあいまいさに戸惑いを感じ、明確な基準が設けられることを望む傾向がある。

65nmプロセスノードには本質的に不確定な要素があるのは確かだ。ガイドラインに十分に従っているかどうかを判断するのは困難だが、すべてに従うことができないことも分かっている。このことから、リスクに対する対処法には設計者によって違いがあるという結果になった。リスクを進んで負う設計者もいれば、文化的な背景によるものか個人的な理由なのかは分からないが、ツールや専門家の指示になるべく従いたいと思う設計者もいる。これは、グローバルな設計リソースの管理においても考察すべき問題となりそうである。

DFMに関するその他の記事

EDNの姉妹誌Electronic Business7月号では、チップ設計のコストが爆発的に増大するであろうDFM以降の展望について調査している。設計や製造にコストがかかりすぎて、カスタムチップは非経済的となり、汎用チップが主流となるであろうという見方まである。

これを信じるか否かは自由だが、設計と製造の関係が劇的に変化していることだけは間違いない。詳細についてはwww.eb-mag.com/dfm0706を参照していただきたい。

Copyright © ITmedia, Inc. All Rights Reserved.