新世代パワーMOS FETの制御と保護:高性能デバイスの特質を最大限に生かす!(1/3 ページ)

パワーMOS FETの進化に伴い、それを制御する側の設計に新たな課題が生じてきた。より高性能な機器の実現が可能になった半面、従来はケアする必要がなかった事柄にも留意しなければならなくなったのである。本稿では、筆者らがオーディオ用D級アンプ向けのPWMコントローラIC製品で実際に用いた技術の解説を通して、新世代パワーMOS FETの特質をフルに引き出す方法を明らかにする。

デバイスの進化、新たな課題

PWM(pulse width modulation:パルス幅変調)を利用したパワー制御/電力増幅技術は、高効率電力変換の基幹技術としての需要の高まりを受け、あらゆる電力制御に幅広く利用されている。DC-DCコンバータやモーター駆動などの高効率化に用いられているほか、最近ではオーディオ用D級アンプなどにも活用されている。

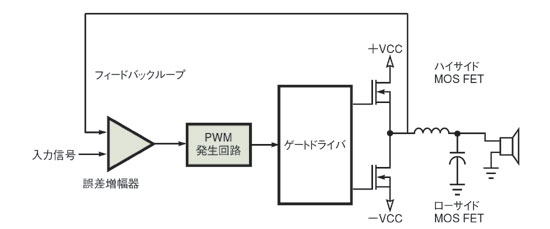

PWMアンプによる電力制御では、ハイサイド/ローサイドのパワーデバイスを交互にオン/オフさせる(図1)。そのため、原理的にはこの部分での電力損失は発生しない。しかしながら、現実の電力効率はパワーデバイスの性能に依存する。MOS FETを例にとると、まずトランジスタがオンした際のドレイン‐ソース間のオン抵抗によって決まる導通損失が発生する。また、オンとオフの切り替えにかかる遷移時間により遷移損失が生じる。

MOS FETは、単位面積当たりのオン抵抗が下がる方向で進化してきた。これにより、導通損失を減らすことが可能になった。また、MOS FETのオン抵抗が相対的に小さくなったことで、トランジスタの面積も小さく抑えられるようになった。その結果、ゲート容量が小さくなり、スイッチングスピードが高速化して遷移損失が低減された。すなわち、PWMアンプの効率は、パワーデバイスが理想的な素子に近づくほど高まることになる。そのため、半導体メーカーはより高性能なパワーデバイスの開発に向けてしのぎを削り、日夜改善を行っている。

ところが、MOS FETの高性能化が進むに連れ、従来は問題視されていなかった事柄が新たな課題として浮かび上がってきた。デバイスの基本性能向上の裏に潜んでいた以下のようなことが、PWMアンプの性能を左右するものとして顕在化してきたのである。

- スイッチングスピードの向上により、ノイズの発生量が増加する

- シリコンチップの小型化により定格外での強度が低下する

- スイッチングタイミング精度を改善しなければ、直線性を改善できない

つまり、パワーMOS FETの進化に伴い、デバイスの保護や制御に対して、これまで以上に留意して臨む必要が出てきたということである。

本稿では、新世代のパワーMOS FETを活用する上で生じる新たな課題に対し、筆者らが行ったチップ設計面での取り組みを紹介する。ここで取り上げる手法は、International Rectifier(IR)社が開発したD級オーディオアンプ用PWMコントローラIC「IRS20955S」で実際に使われているものである。同製品とパワーMOS FET(別掲記事「『新世代のパワーMOS FET』とは?」を参照)を用いて構成したオーディオ用D級アンプの評価結果を示すことで、その効果も明示したい。これを通じて、新世代パワーMOS FETのメリットを最大限に引き出すための設計アプローチを明らかにする。

スイッチングノイズの影響を抑える

まず、スイッチングスピードの向上によりノイズの発生量が増加するという問題について考えてみる。スイッチングノイズ電圧Vnは、主に電流切り替え遷移速度di/dtと浮遊インダクタンスLに比例して発生する(以下参照)。

素早いスイッチング動作は、より大きなdi/dtを発生させ、結果として電流ループ内に存在する浮遊インダクタンスLの両端に、より大きなノイズ電圧Vnを誘起する。発生するノイズの中で最も有害な成分は、MOS FETのゲートを駆動する信号の制御系に流入するノイズだ。流入するノイズの量が限界を超えると、想定外のタイミングでゲートがオンしたり、ジッターが発生したりするなどして、システム性能の劣化や誤動作という結果を招く。

高速化が進む新世代MOS FETのメリットを生かすためには、より高い時間精度でMOS FETをコントロールしたい。例えば、スイッチング周波数を高めて誤差増幅器の帯域を広げれば、制御周波数範囲が広がり、高速に負荷を駆動することができる。このような場合、PWMアンプの制御系は広いループゲインを持つので、ノイズの多いスイッチング段の影響を受けやすくなる。つまり、MOS FETの高速化によって増加するスイッチングノイズに対応するために、ノイズに対するアイソレーション(絶縁)を一層強化する必要が出てきたということだ。

従来の対処策の問題点

2つのMOS FETで出力段を構成するハーフブリッジ型を例に、ノイズの混入を防ぐ方法を考える。図2に示すように、出力段のスイッチング動作により、ゲートドライバの動作基準電位はスイッチングノイズで“汚染”される。一方、PWM信号はクリーンなグラウンド(GND)を基準として生成される。つまり、スイッチングノイズによって汚れた動作基準電位を基に動作するゲートドライバに、いかにして精度の高いPWM信号を伝達するのかということがここでの命題となる。

まずは、一般的な対処法について見てみよう。図3に示したのは、外付け回路を用いてノイズアイソレーションを実現している例である。この回路において、ゲートドライバはローサイドMOS FETが接続された負電源(−VCC)を基準として動作する。そこで、PWM信号をグラウンド基準から負電源基準にレベルシフトする際にノイズアイソレーションを実現する。具体的には、バイポーラトランジスタの高い出力抵抗を利用してPWM信号をいったん電流に変換して送り出し、負電源基準に接続された外付けの固定抵抗によって電圧情報に戻してゲートドライバに入力する。この方法では、パイポーラトランジスタや抵抗などの外付け回路を必要とする点がデメリットとなる。

「新世代のパワーMOS FET」とは?

本稿で示す評価結果は、PWMコントローラICであるIRS20955SとIR社の「IRF6645」を組み合わせて構成した出力120WのD級アンプのオーディオ特性である。本稿でいう「新世代のパワーMOS FET」とは、IRF6645のように、オーディオ用アンプに代表されるような高精度の要求に応える高いレベルの性能を備えた製品のことを意味する。

IRF6645はトレンチ構造のパワーMOS FETであり、そのオン抵抗は35.0mΩ以下に抑えられている(ゲート‐ソース間電圧が10Vのとき)。また、THD+Nや効率に影響するゲート入力電荷量Qgも14nC(標準値)と小さい。

同製品の特徴の1つとして、IR社独自の小型金属パッケージ「DirectFET」に収められている点が挙げられる。同パッケージでは、MOS FETのシリコンチップを直接プリント基板に半田付けできるようになっている。そのため、浮遊インダクタンスが付加されにくく、リンギングやEMIノイズが発生しにくい。これにより、MOS FETの性能が最大限に引き出せるようになっている。

Copyright © ITmedia, Inc. All Rights Reserved.