新世代パワーMOS FETの制御と保護:高性能デバイスの特質を最大限に生かす!(3/3 ページ)

パワーMOS FETの進化に伴い、それを制御する側の設計に新たな課題が生じてきた。より高性能な機器の実現が可能になった半面、従来はケアする必要がなかった事柄にも留意しなければならなくなったのである。本稿では、筆者らがオーディオ用D級アンプ向けのPWMコントローラIC製品で実際に用いた技術の解説を通して、新世代パワーMOS FETの特質をフルに引き出す方法を明らかにする。

シャント抵抗を使わずに過電流を検出

IRS20955Sでは、MOS FETがオンした際のドレイン−ソース間電圧をモニターする回路を用いて過負荷保護を実現している。この方式には2つの利点がある。

第1の利点は、外付けのシャント抵抗が不要なことだ。これにより、上述した外付けシャント抵抗のデメリットが発生することはなくなる。

第2の利点は、過電流検出をPWMコントローラICに内蔵された機能とすることで、重畳されたリンギングなどのノイズの影響を容易に除去できることだ。確かに、スイッチング動作を伴うPWMアンプはノイズの発生源には違いない。しかし、そのノイズはスイッチング動作を行ったときにしか発生しない。つまり、スイッチングとスイッチングの間は“静か”なのである。過電流検出機能をPWMコントローラICに内蔵した場合、この静かな瞬間に電流をサンプリングすることができる。サンプリングにより過電流を検出する方法であれば、前述した誤動作防止用のLPFを大幅に軽くでき、過負荷保護回路を高速化することが可能なのだ。

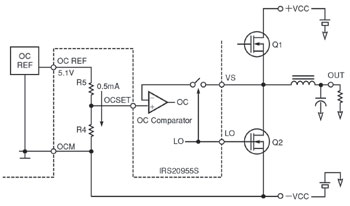

図7に示したのは、IRS20955SのローサイドMOS FETの過電流検出回路である。この図を基に、同製品における過電流検出方法について説明する。

過電流の検出は、ローサイドMOS FETがオンしたときのドレイン‐ソース間電圧をモニターすることで行う。ゲートドライバは、ローサイドMOS FETのソース電極を基準にして電圧を出力する。つまり、ゲートドライバの動作の基準点は、ソース電位COMである。また、IRS20955SにはハイサイドMOS FETを駆動するために、そのソース電極にアクセスするための端子VSが存在する。これをローサイドMOS FETのドレイン電位のモニター用に利用する。

ゲートドライバがローサイドMOS FETをオンにすると、そのドレイン電圧が降下する。過負荷保護回路は、スイッチング動作時の遷移時間を考慮し、ローサイドMOS FETが完全にオンしてからドレイン電圧をモニターする。そのドレイン‐ソース間電圧を与えられた閾値OCSETと比較し、ドレイン電圧が過大であれば過電流が発生したと見なして保護回路を動作させるという仕組みだ。

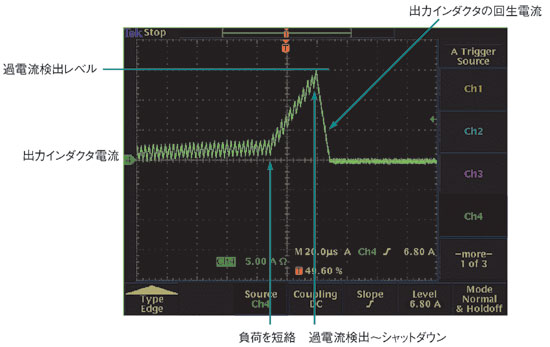

図8は、この過負荷保護回路の動作の様子を表している。ドレイン‐ソース間電圧が閾値である0.6Vを越えた瞬間にシャットダウンし、パワーMOS FETを保護していることが見てとれる。この過負荷保護回路のトリップ値は20Aで、検出からシャットダウンまでにかかる時間は300nsである。

なお、オーディオ用D級アンプでは負荷電流が両極性となる。そのため、IRS20955Sには、ハイサイドMOS FET用にも同様の過電流検出機構を設けている。

PWMアンプの直線性を高める

PWMコントローラでは、PWM出力段の上下2つのMOS FETが同時にオンして電源がショートする(シュートスルー現象)のを防ぐために、同時にオフする期間を意図的に設ける。これを「デッドタイム」と呼ぶ。

例えば、オーディオ用のPWMアンプでは、負荷電流の極性が交互に変化する。このようなアプリケーションでは、デッドタイムを挿入することが原因で、負荷電流の極性が変わる付近で出力に非直線性が生じるという問題がある。デッドタイムによって直線性が劣化する理由は、デッドタイムの期間中には、PWM出力の状態が、ゲートドライバからの指示ではなく、負荷電流によって決定されるからである。逆に、PWM出力段の非直線性はデッドタイムによる影響が支配的なので、この出力不定状態を生じさせるデッドタイムを短くすることが出力段の直線性の改善につながる。言い換えれば、デッドタイムが少ないほど直線性が良く、歪の少ない増幅が行えるということだ。

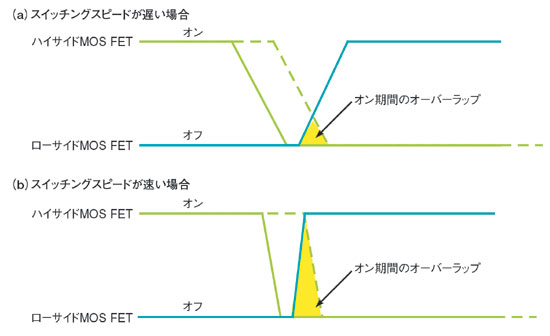

新世代のMOS FETは、オン/オフの遷移時間が短い。従って、原理的にはデッドタイムを短く設定することが可能であり、PWMアンプの直線性を根本的に改善することができる。しかし、実際にはスイッチングスピードが速いため、デッドタイムの設定値が短く、その値がばらついてしまうと、出力段の2つのMOS FETへのゲート駆動パルスがオーバーラップし、MOS FETが同時にオンして大電流が流れてしまうことがある。スイッチングスピードが速いMOS FETは、遅いMOS FETよりもデッドタイムの変動に対して敏感となる。すなわち、オーバーラップが同じだけ生じた場合、スイッチングスピードが速いほうが、より大きな電流が流れる(図9)。従って、シュートスルー現象が起こらないよう、デッドタイムをきっちりと管理し、ゲート駆動パルスのタイミングを高精度化する必要がある。それにより、初めてスイッチングスピードの高速化を直線性の改善策として生かせるようになる。

また、デッドタイムの設定方法としては外付け抵抗を用いる方法が考えられるが、この点にも注意を払う必要がある。直線性を良くするために、デッドタイムは小さくしたい。しかし、デッドタイムが小さくなると、より小さなばらつきによりシュートスルー現象が発生する。つまり、与えられたMOS FETで最大限の直線性を得るには、MOS FETのスピードに合わせてデッドタイムを設定する必要があるが、外付け抵抗によってデッドタイムを設定する手法は最適ではない。IC内部の回路と外部抵抗のばらつきにより、デッドタイムの精度を上げにくいからだ。従って、ここにも新たな設計を導入する必要がある。

デッドタイムを高い精度で管理する

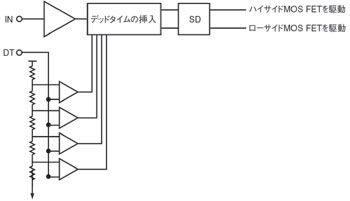

IRS20955Sは、デッドタイムの発生回路を内蔵している。この回路では、ディレイマッチングなど、デッドタイムがずれる要因を自己補正でき、デッドタイムの制御が高精度に行えるようになっている。

図10に示したのが、デッドタイム発生回路のブロック図である。MOS FETに実際に働くデッドタイムは、ローサイドMOS FETが完全にオフしてからハイサイドMOS FETがオンし始めるまで、またはその逆の期間である。この方式の場合、ハイサイド側のゲート駆動出力までの伝播遅延時間と、ローサイド側のゲート駆動出力までの伝播時間をいかに精度良く管理できるかが、そのままデッドタイムの精度に影響する。IRS20955Sでは、それぞれの伝播時間をできるだけ等しくするために、差分を調整する回路ブロックを挿入してバランスをとることで、デッドタイムの精度を上げている。

また、IRS20955Sには、デッドタイムの設定方法の面でも工夫を盛り込んでいる。チップ内部の抵抗を用いてデッドタイムを何種類か設定できるようにしておき、その中から選択できるようになっているのである。この方法であれば、外付け抵抗の誤差など、外部の変動要因がデッドタイムに影響せず、安定した精度が得られる。

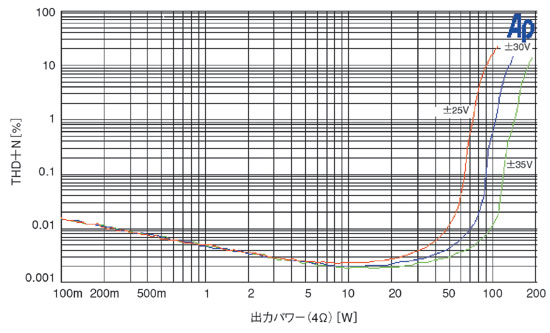

以上の方法を用いることにより、デッドタイムを小さい値に設定して、PWMアンプの直線性を改善することができる。図11は、IRS20955Sを用いて構成したオーディオ用アンプのTHD+N(total harmonic distortion plus noise:全高調波歪率)特性を表している。THD+Nは、増幅器の直線性を表す指標となる。従って、これを見れば、このオーディオ用アンプが広範な出力パワー領域にわたって、非常に良好な直線性を実現していることが分かる。また、この結果は、ゲートコントローラへのスイッチングノイズの混入を防ぐノイズアイソレーション手法が成功していることも併せて示唆している。

進化に応じた新たな設計

ここまで述べてきたように、新世代パワーMOS FETの特性を生かすには、その高速化されたスイッチング性能と小型化されたシリコンチップを取り扱うための新しい設計上の配慮が必要である。本稿では、オーディオ用D級アンプ向けのPWMコントローラICを例にとり、そうした新たな設計手法をいくつか示した。

高性能かつ安定したPWM出力段を実現することにより、機器の設計者にとって開発しやすい環境を提供することができる。それにより、設計者は誤差補正方式の設計や、コントロールループの最適化といったPWMアンプ制御の差異化のための本来業務に時間を割けるようになる。そのことが、より優れた機器を、より早く市場に投入することにつながるのである。

Copyright © ITmedia, Inc. All Rights Reserved.