低価格FPGA開発キットの実用性を探る:主要4製品の使い勝手を実践検証!(3/5 ページ)

FPGAは、通信/産業の分野で圧倒的優位に立った。それに続き、FPGAベンダーは自動車やコンスーマ機器などの市場をも制覇しようともくろんでいる。そのために鍵となるのは、FPGAそのものの実力もさることながら、開発キットの価格と使いやすさである。本稿では、低価格のFPGA開発キット4製品をピックアップし、その実用性を検証する。

MAX II開発キット――Altera社

ほぼ15年間にわたりCPLD市場をリードしてきたAltera社は、「MAX II」ファミリに今でもこの「CPLD」という言葉を使い続けている。このMAX IIファミリは240〜2210個のLE(ロジックエレメント)を搭載した4つの製品で構成されている。その能力は一般のCPLDで使用されるマクロセルに換算すると192〜1700個に相当するという。パッケージの種類は100端子TQFPから324端子BGAまでが用意されており、ユーザーが設定可能な最大I/O数は80〜272となっている。ホットスワップ可能なI/Oを備えたデバイスがサポートしているI/O電源は1.5V、1.8V、2.5V、3.3Vで、コアロジックの動作電圧は1.8Vである。

そのほかの特徴として、プログラム可能なシュミットトリガー入力と、3.3V/66MHz動作のPCI 2.2と互換性のあるI/Oを備えることが挙げられる。デバイス内部のフラッシュメモリーは即時処理を可能にするコンフィギュレーションデータを保持し、ユーザーデータ用にも8Kビットの領域を確保している。

FPGAとCPLDの違い

Altera社のMAX IIデバイスはルックアップテーブル(lookup table。以下、LUT)方式を採用していることから、CPLDというよりもFPGAに近い感がある。Altera社で低価格製品のシニアマーケティングマネジャを務めるDenny Steele氏は、「そもそもCPLDとFPGAとでは、出力の生成方法が異なる」と説明する。

「従来のCPLDは、一般にアドレスデコーダなどの用途に最適なAND/ORアレイを採用している。一方のFPGAには、4本のアドレスラインで論理機能を実装する4入力のLUTアーキテクチャが採用されている。この方式であれば算術演算を非常に高速に実行できるため、DSPや通信用途において自然にFPGAが普及していった」(同氏)。

Steele氏は、両者のもう1つの大きな違いとして、「CPLDではすべてを接続するクロスポイントスイッチ配線方式が使用される。それに対し、FPGAではセグメント単位の配線方式が使用されるため、大規模ロジックブロックが直接かつ決定的に接続される」ことを挙げた。

PCIとUSBを備えた評価ボード

MAX IIファミリのCPLD「EPM1270」に対応したAltera社のMAX II開発キット(単価は150米ドル)には、評価ボードとパラレルポートダウンロードケーブル「ByteBlaster II」、そしてボードとパソコンホストを接続するためのUSBケーブルが付属している。

この評価用ボードはPCIボードの形状を成しており、CPLDデバイスと米Cypress Semiconductor社製の1MバイトSRAMのほか、CPLDの電力消費量を監視する電流測定回路を組み込んだA-Dコンバータを接続できるようになっている。加えて、このボードは16文字×2ラインを表示可能な液晶とLED、スイッチ、端子ヘッダー、USB/PCIインターフェースを備えている。2枚のCD-ROMが添付されており、1枚にはWindows NT/2000/XP対応の統合開発環境「Quartus II(以下、Quartus)」が収録されている。もう1枚は、電子版ガイド「Getting Started」を含むドキュメントを収録している。

MAX IIの内部構造

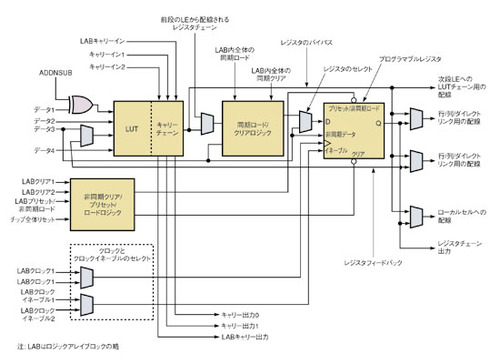

MAX IIファミリのEPM1270には、127個のLAB(ロジックアレイブロック)が行列構造で配置されている。各LABは10個のLEで構成され、各LEは4入力のLUTと周辺のLEへの制御/フィードバック/配線用リソースで構成されている(図3)。LUTにより、すべてのLEに4入力機能を持たせることができる。

キャリーチェーンブロックは、複数のLEを使用した高速演算を可能にする。出力信号は隣接するLEに直接配線することもできるが、ローカル/グローバル配線に接続することも、あるいはプログラマブルレジスタ経由で配線リソースに渡すことも可能である。

動作モードには「通常モード」と「ダイナミック演算モード」の2種類があり、Quartusに付属するコンパイラによって通常の論理演算または算術演算(加算器、減算器、カウンタ、アキュムレータ、およびコンパレータなど)に最適なモードが選択される。高速なローカル相互接続システムによって同一のLAB内で隣接するLE間の信号を受け渡し、行列間の相互接続システムによってグローバル接続を可能にしている。

Quartusのインストール

開発キットを利用するには、ソフトウエアをインストールしなければならない。まず、スタータキットをインストールし、Altera社のウェブサイトからライセンスを入手する。次にアップデートがないかどうかを確認した上でQuartusをインストールする。今回は、CD-ROMに収録されているバージョン5の代わりに、バージョン6 SP1をダウンロードして使用した。システムソフトウエアをインストールするときは必ず「Talkback機能」を選択し、組み込みロジックアナライザ「SignalTap」、「SignalProbe」、「FastFit機能」を有効にできるようにしておく。

機能は充実、ヘルプには不満も

この開発ボードへの電源は、PCIインターフェースとUSBインターフェースのうちどちらかを選択して供給できる。PCIに接続せずに開発するのであれば、ジャンパJ8の1-2を選択する。これによってUSBから電力を供給する設定になる。このボードに実装されているEPM1270には、ボードのハードウエアの動作確認用テストプログラムがあらかじめ書き込まれている。Byte Blaster IIを使用すれば、このコードを足掛かりにしてデバイスを再プログラムすることも可能である。スタータキットのexamples\HW\demosディレクトリには、3つのデモが格納されている。それぞれ、起動時のタイミング特性、消費電力の低さ、リアルタイムISP機能を示すためのデモである。ここでいうリアルタイムISPとは、デバイスがすでに構成(コンフィギュレーション)されている場合に、その回路の動作中に新たなプログラムを内部フラッシュメモリーに書き込むことができるということを表す。スイッチS5を押すとコア部の電源が遮断され、バックグラウンドで書き込まれたプログラムによってデバイスが再構成される。

これらのほかに、チュートリアルにはUSBとPCIインターフェースのリファレンス設計と、スロットマシンのサンプルが含まれている。これらのうちUSB用のサンプルだけに、入力方法を示すためのVerilog HDLソースがある。

しかし、残念なことにすぐ学習に役立つ材料はここまでのようだ。Quartusのヘルプメニューには、Quartusの使用方法をステップバイステップで学習できるチュートリアルのほか、VerilogとVHDLの入門ガイドが含まれてはいるが、学習ツールとしてはお粗末といわざるを得ない。例えば、チュートリアルでは設計のプロセスを順に追って進めていくが、それらのプロセスがなぜ必要なのかという説明がない。筆者は2時間以上をかけて不可解なステップをくぐりぬけ、ようやくコンパイルステージにたどり着いた。しかし、hvalues.vファイル内で致命的なポート宣言エラーが発生し、最初の試みは失敗に終わった。このファイルはチュートリアルの指示に従ってコピーしたものだ。その後2回試みたが、いずれも失敗した。Altera社のウェブサイトでは、一般的なものから特殊なものまで数多くの設計サンプルが提供されている。しかし、初心者がスタートを切るための簡単なガイドは存在しないようだ。筆者のように初めて利用する者にとっては、ビギナー向けのチュートリアルがないQuartusは非常に分かりにくい。260ページ以上もある「Introduction to Quartus II」というマニュアルにも、総ページ数2160ページの「Quartus II 開発ソフトウエアハンドブック」の5冊セットにも、そうしたヘルプは一切ない。

とはいえ、理解力、経験、あるいは時間に恵まれているユーザーであれば、間違いなくQuartusのパワーにのめりこむことになるだろう。ブロックをシンボリックに入力する機能、標準ライブラリの豊富さ、さらにはそのまま使用することもカスタマイズすることも可能なビルド済みの「メガファンクション」など、非常に魅力的な要素を備える。あるいはディスクリートロジックの愛好者ならば、74シリーズのTTLライブラリに興味を持つはずだ。

Copyright © ITmedia, Inc. All Rights Reserved.