ESD対策新時代(3/4 ページ)

携帯電話端末に代表される電子機器の高速化、低消費電力化などに対応するために、新しいデバイス構造を採用した製品の開発が進んでいる。しかし、そうした構造はESDに対し脆弱であることが確認されており、従来の手法では不十分となってきた。本稿では、新たなデバイス構造にも対応可能な最新のESD保護回路設計についてまとめる。

ESD耐性に劣る先端デバイス構造

ここまで、代表的なESD損傷モデルと従来の保護回路について説明してきた。しかし、近年では上述した方法によって良好なESD耐性を実現するのは困難になってきている。その原因は、本稿の冒頭で述べた通り、先端半導体デバイスの構造が変化したことである。先端半導体デバイスは、急速な性能向上の要求に対応するために新たな構造を採用してきた。結果として、その構造上の変化が、単純な微細化によるESD耐性の低下とは異なる、各種ESDモデルに特有の脆弱さをもたらすことになったのだ。ここでは、HBM耐性を例にとり、それについて説明を行う。

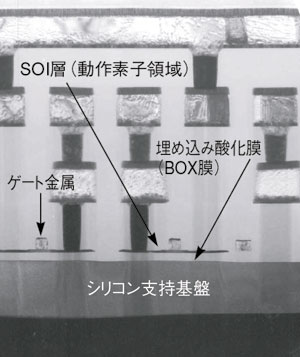

写真4に示したのは、高速化、低消費電力化を実現するトランジスタとして用いられるFD-SOI(fully depleted silicon on insulator)構造デバイスの断面である。シリコン支持基板とSOI層(動作素子領域)は埋め込み酸化膜によって分離され、また素子間も酸化膜によって完全に分離されている。そのため寄生容量が非常に小さく、SOI層が非常に薄く完全に空乏化しているので、高速動作、低電圧動作、低消費電流動作が可能になる*9)。

ところが、この薄いSOI層にHBMサージが流入してブレークダウンが起きると、周囲が熱伝導性の悪い酸化膜であるが故に、発熱した熱がほとんど逃げず、ポリシリコン抵抗の溶断現象のように簡単に破壊してしまう。だからといって、SOI層を厚くして酸化膜分離構造を変えると、要求性能が実現できない。すなわち、FD-SOI構造を採用することによって性能を実現しようとするならば、ESDに対する脆弱性を克服するための新たな保護設計手法が必要となる。

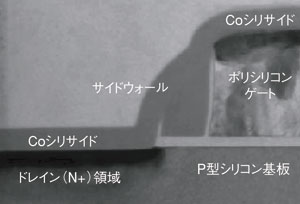

もう1つ例を挙げよう。サリサイド構造により高速化を図ったトランジスタを採用している先端デバイスにおいても、FD-SOI構造のデバイスと同様なことがいえる(写真5)。

サリサイド構造とは、ソース/ドレイン領域のシリコン層、ゲートポリシリコン層に、融点の高い金属(写真5ではコバルトCo)との化合物を形成することにより、抵抗成分による遅延を低減し、高速動作を実現するというものである。

しかしながら、この構造を用いたトランジスタでは、HBMサージなどによる電荷がドレインに流入したとき、ドレイン領域の底面からシリコン基板へ電荷を分散させることができない。言い換えれば、実効接合断面積が極端に小さくなるため、1カ所がブレークダウンすると、HBMサージによる電荷がすべてそこに集中して破壊に至る。この場合、トランジスタの接合面積を増加させても耐性は向上せず、保護回路を構成できない。

上述した理由から、ゲート側のドレイン、ソース部分のサリサイドを除去した領域(サリサイドブロック領域)を形成することによって、ブレークダウン時の実効接合断面積が確保されるようにしたトランジスタが考案された。これを出力トランジスタや電源間保護トランジスタ(PC:power clamp)に使用することが、ESD(HBM)耐性を向上させる方法として考えられる。しかし、このサリサイドブロック構造のトランジスタは、各種ESDサージに対する応答が遅いため、保護されるべき内部回路に電荷が流入し、保護回路としての役目を果たせなくなってしまう場合がある。かといって、内部もサリサイドブロック領域を用いた構造にしたのでは、最初からサリサイド構造を採用しないのと同じことになり、高速性能の実現を放棄することになってしまう。

先端のデバイス構造を採用することによるESDに対する脆弱性は、高耐圧素子などさまざまなケースで見られる。そうした構造を用いた半導体デバイスのESD耐性を確保するために、ESD保護設計手法の新規構築という大きな変革が必要となったのである。

新たなESD保護設計手法(1)――Mixed Modeシミュレーションの利用

新たなESD保護設計手法の例として、本稿では、サリサイド構造デバイスにおけるESD(HBM)保護の手法を示すことにする*10)、*11)。

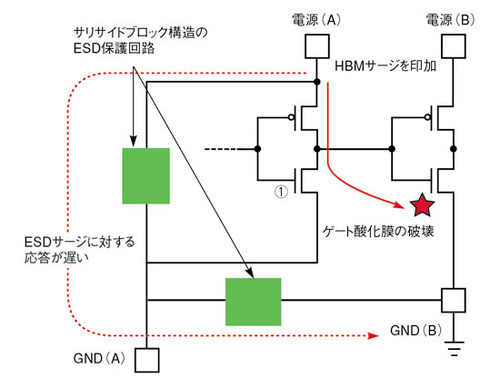

図9に示したのは、分離電源方式のチップにおける、サリサイドブロック構造のトランジスタを用いたESD保護回路の例である。この回路において、GND(B)端子を基準として電源(A)端子にHBMサージを印加する試験を実施したところ、電源(A)、(B)に対応する回路ブロック間で信号を伝達するトランジスタ(図中の(1))のゲート酸化膜が500V〜1000Vで破壊した。その原因は、電源(A)‐GND(A)間、GND(A)‐GND(B)間にサリサイドブロック構造の保護トランジスタ(PC)が挿入されているものの、それらがHBMサージによる電荷を逃がすまでの応答時間が長いため、(1)のトランジスタのゲート酸化膜に過渡的な電圧が印加されて破壊したものと推定される。

この種のESD保護においては、ESD耐性の改善度と性能の低下との間のトレードオフ関係について事前に見積もる必要がある。それには、各素子のESDイベントに対応する動作パラメータ(ESDパラメータ)を抽出し、それを用いたESDシミュレーションの実施を可能にする手法を構築しなければならない。その結果、対策案の検討を机上で行えるようになり、ESD保護性能と製品性能の最適化が実現できるのである。

筆者ら(沖エンジニアリング)は、TDR(time domain reflection)-TLP(transmission line pulse)測定方法によりESDパラメータの抽出を行い、デバイスシミュレーションと回路シミュレーションを混合したMixed-Modeシミュレーションを用いることによって上述した手法を実現した*12)。以下、その概要を紹介する。

このMixed-Modeシミュレーションでは、ブレークダウン後の領域とトランジスタのスナップバック領域の特性をデバイスシミュレーションとして合わせこむというモデリングを行っている。また、そうした個々のデバイスシミュレーションモデルを簡単な等価ESD回路モデルとして接続することでシミュレーションが行えるようなモデリングも行っている。本Mixed-Modeシミュレーションでは、これら2つのESDモデリングが肝となっている。

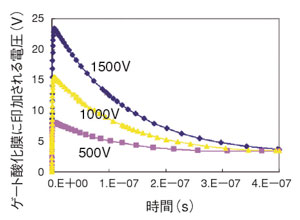

図10は、HBMの各印加電圧において、図9のトランジスタ(1)のゲート酸化膜にかかる過渡電圧をMixed-Modeシミュレーションした結果である。この図の縦軸は、当該ゲート酸化膜にかかる電圧を表している。ゲート酸化膜の真性破壊電圧は14Vなので、図10は500V〜1000VのHBMサージ印加電圧によって当該ゲート酸化膜が破壊することを表現できているものと考えられる。

次に、このESDモデリング/Mixed-Modeシミュレーションを利用して、耐性を向上させるための対策方法を検証する。対策案としては、以下の2つが考えられる。

(1)破壊されたゲートのノードに、ゲート破壊防止用の抵抗を挿入する

(2)破壊されたゲートとGND(B)端子の間にGGnMOS保護トランジスタを挿入する

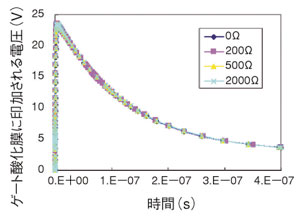

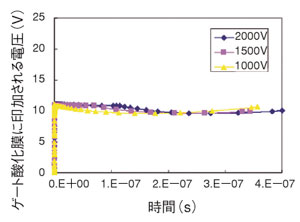

図11は、HBMで1500Vを印加した際、上記(1)の条件で、抵抗値を変更した場合に当該ゲート酸化膜に印加される過渡電圧を表している。一方、図12は、(2)の条件において、当該ゲート酸化膜に印加される過渡電圧を表している(印加電圧は2000V、1500V、1000V)。2つの結果から、(1)のゲート破壊防止抵抗は何の対策効果も持たず、(2)のGGnMOS保護トランジスタの挿入が非常に有効な対策であるということが検証できる。

このように、TDR-TLP測定によるESDパラメータ抽出、ESDモデリング、Mixed-Modeシミュレーションを用いる手法は、破壊が生じないような各種ESDサージ経路を検証しながら設計が行えるという、非常に効果的な新ESD保護設計手法である。

脚注

※9…福田保裕、ほか, "SOI-CMOSデバイス技術", 沖テクニカルレビュー誌, 2001年1月/第185号Vol.68 No1

※10…H.Hayashi atc, "ESD Protection Design Using a Mixed-Mode Simulation for Advanced Devices", 2004 EOS/ESD Symp proc. 2B.4

Copyright © ITmedia, Inc. All Rights Reserved.