次世代アナログLSIでは、素子モデルの標準化が急務(1/4 ページ)

プロセスの微細化は、アナログ混載LSIの設計手法にも大きな影響を与えている。最も重要なのは、新たなプロセスに対応した高精度の素子モデルを開発し、それを標準化することである。本稿では、まずこの標準化にかかわる動向をまとめる。その上で、微細プロセスを用いたアナログ回路設計手法を確立するためのその他の課題を指摘する。

求められる新・標準モデル

この20年の間に、アナログ混載LSI(ミックスドシグナルLSI)は一般的なものとなった。アナログ回路とデジタル回路の両方を1つに集積したLSIに対するニーズは高い。

その一方でエレクトロニクス業界には大きな変化が訪れた。LSIの設計から製造までを自社で行うIDM(integrated device manufacturer:垂直統合型デバイスメーカー)モデルから、システム企業がLSIの設計までを行い、ファウンドリ企業にチップの製造を委託するファブレスモデルへと大きく移行したのだ。

ムーアの法則に従って集積度が高まるに連れ、こうした傾向は強まった*1)。そうした中、システム企業が開発した設計データに基づいて、ファウンドリ企業が堅牢なチップを製造するのが困難になってきた。従来から使用されてきたシミュレーション用のコンパクトモデルには、素子の動作記述の点で限界があり、もはや設計者はそれに頼ることができなくなった。ファブレス企業の回路アプリケーションは広範囲にわたり、従来のコンパクトモデルで検証できる範囲を超えている場合が多いのだ。

従来のIDMモデルでは、各企業は独自のアプリケーションやシミュレーションツール、設計フロー/手法に合わせて作成されたモデルとシミュレーションプラットフォームを使用して独自の手法で開発を行っていた。それに対し、ファブレスモデルでは、IDM、ファウンドリ、ファブレス企業におけるすべての条件を網羅するコンパクトモデルの標準セットを考案することが求められている。こうした状況を踏まえ、CMC(Compact Model Council)などいくつかの専門組織が、この要求を満たすべく活動を行っている。

BSIM3モデルの限界

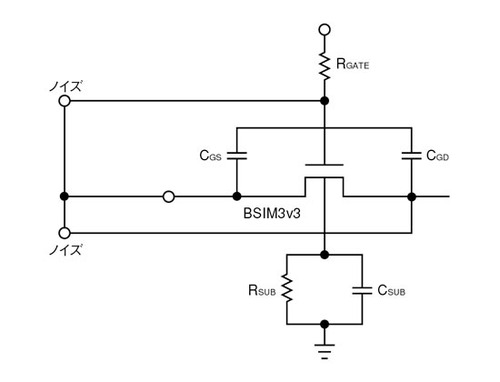

CMCは、カリフォルニア大学バークレー校が開発したBSIM3(berkeley short-channel IGFET model 3)Version 3(以下、BSIM3v3)のMOS FETモデルを、1996年に業界標準のMOS FETモデルに選定した(図1)*2)。標準となったことで、このモデルは主要なシミュレーションプラットフォームで使われるようになった。その結果、あるシミュレータから別のシミュレータへと比較的スムーズに移行できるようになった。これまで技術は大きく移り変わってきたが、その間もこのモデルで十分であった。

図1 BSIM3v3モデル MOSFETでは、BSIM3v3モデルが標準となっている。しかし、RFアプリケーションなどで利用するには、ゲートの抵抗成分や寄生容量、ノイズ源などを表現できるよう、サブ回路内に実装可能な寄生集中定数素子を用いてモデルを拡張しなければならない。標準化が行われていないと、この作業の過程やシミュレータ間での移行時に誤りが生じる可能性がある。

しかし、トランジスタの微細化が進んで電源電圧が低下したことに伴い、BSIM3v3モデルでは新たな物理的影響を記述する能力や精度が不足しているという事実が問題となってきた。BSIM3モデルを用いた開発は、すべての電圧がソース電位を基準とする、MOS FETのレベル3モデルの手法をベースとする。主なパラメータは閾(しきい)値電圧であり、ゲート‐ソース間の電位差が閾値電圧と等しくなったときに反転層が生じて導電チャンネルが形成されるというモデルである。別の動作は別の関数でモデル化するが、その手法では閾値に依存したこの動作を表す関数が不連続になる。このことが、アナログシステムや高周波数システムの設計においては大きな問題となる。 BSIM3では、サブスレッショルド領域と強反転領域の間の動作に平滑化関数を導入することにより、電流/電圧特性の不連続性をなくした1つの関数式を提供している。これによって不連続性の問題は解決される。ただし、平滑化関数は経験によって得られたものなので、弱から中程度の反転領域でのモデルの精度の面で限界がある。そのため、アナログシステムの設計では、短チャンネル効果の影響を受けず、強反転領域で飽和した状態に保つことが可能な大きなサイズのトランジスタを用いるのが一般的である。

この手法は、閾値電圧VTHに対して電源電圧VDDが十分に高く、それにより電圧範囲に対する動作マージンが大きく確保されていた時代にはうまく機能していた。しかし、最新の半導体プロセスでは、VDDとVTHの差が非常に小さく、うまくモデル化されていない弱から中程度の反転領域でMOS FETを動作させなければならない。また、コスト削減の要求に対応するために、短チャンネル効果が発生する小さなMOS FETが使用される。

以上のことから、素子の動作を「2乗法則(square law)」のような簡単な記述では表現することができなくなった。ここでいう2乗法則とは、以下の式で表される関係のことである。

ここで、IDSはドレイン‐ソース間電流、VGSはゲート‐ソース間電圧、μはキャリアの移動度、Wはチャンネル幅、Lはチャンネル長、COXはゲート容量である。

現行のVTHモデルでは、例えば高周波ノイズのモデリングや、ダイナミックレンジが大きい電流の正確な記述といった問題にうまく対応できない*3)。今求められているのは、弱から中程度の反転領域の動作に対応可能な正確なモデルである。

脚注

※1…International Technology Roadmap for Semiconductors.

※2…BSIM3/BSIM4 Industry Standard for Circuit Design.

※3…Gildenblat, Gennady, and T-L Chen, "Overview of an Advanced Surface-Potential-Based Model," Nano Science and Technology Institute, Fifth International Conference on Modeling and Simulation of Microsystems, April 2002.

Copyright © ITmedia, Inc. All Rights Reserved.