‘g‚فچ‚ف•sٹِ”گ«ƒپƒ‚ƒٹپ[‚جگ³‚µ‚¢‘I‘ًپi1/3 ƒyپ[ƒWپj

SoC‚ة‘g‚فچ‚ف‰آ”\‚ب•sٹِ”گ«ƒپƒ‚ƒٹپ[‚ة‚ح‚¢‚‚آ‚©‚جژي—ق‚ھ‚ ‚éپB‚»‚ꂼ‚ê‚ج“ء’¥‚ً‚آ‚©‚فپA—p“r‚²‚ئ‚ة‹پ‚ك‚ç‚ê‚é—vŒڈ‚ً‹ل–،‚µ‚½ڈم‚إچإ“K‚ب‚à‚ج‚ً‘I‘ً‚·‚邱‚ئ‚ھٹج—v‚إ‚ ‚éپB–{چe‚إ‚حپA‚»‚ج‘I‘ً‚ج‚½‚ك‚جƒKƒCƒh‚ً’ٌ‹ں‚·‚éپB

‘½ژي‘½—l‚ب‘g‚فچ‚فNVM

پ@•sٹِ”گ«ƒپƒ‚ƒٹپ[پiNVMپFnon volatile memoryپj‚ً‘g‚فچ‚ٌ‚¾IC‚جژù—v‚ھچ‚‚ـ‚è‚آ‚آ‚ ‚éپB‚±‚جŒXŒü‚ًŒم‰ں‚µ‚µ‚ؤ‚¢‚é‚à‚ج‚ج1‚آ‚حپAMP3ƒvƒŒپ[ƒ„‚ب‚اپAƒfƒWƒ^ƒ‹’کچىŒ ٹا—‚âƒZƒLƒ…ƒٹƒeƒB‘خچô‚ً•K—v‚ئ‚·‚é–¯گ¶‹@ٹي‚ج•پ‹y‚إ‚ ‚éپB‚ـ‚½چإ‹ك‚ج‹Zڈp‚جگi•à‚ة‚و‚ء‚ؤپAگفŒvژز‚ھ‚³‚ـ‚´‚ـ‚ب•û–@‚إNVM‚ًƒIƒ“ƒ`ƒbƒv‚ة“چ‡‚إ‚«‚é‚و‚¤‚ة‚ب‚ء‚½‚±‚ئ‚à”wŒi‚ج1‚آ‚ئ‚ب‚ء‚ؤ‚¢‚éپB

پ@ڈ—ت‚جNVM‚µ‚©•K—v‚ئ‚µ‚ب‚¢SoCپisystem on chipپj‚جڈêچ‡پAˆê”ت‚ة‚حƒ}ƒXƒNROM‚âƒoƒbƒeƒٹƒoƒbƒNƒAƒbƒvژ®‚جSRAMپAƒAƒ“ƒ`ƒqƒ…پ[ƒYƒپƒ‚ƒٹپ[‚ب‚ا‚ھژg‚ي‚ê‚邱‚ئ‚ھ‘½‚¢پBگفŒv‚ة‚و‚ء‚ؤ‚حپAEEPROM‚âƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹپ[‚ھ‘I‚خ‚ê‚邱‚ئ‚à‚ ‚邾‚낤پB‚ ‚é‚¢‚حپAƒچƒWƒbƒNNVMپiƒچƒWƒbƒN‰ٌکH—p‚ج’تڈي‚جCMOSƒvƒچƒZƒX‚إگ»‘¢‰آ”\‚بNVMپj‚ئ‚¢‚¤‘I‘ًژˆ‚à‚ ‚éپB

پ@‚±‚¤‚µ‚½•ûژ®‚ة‚حپA‚»‚ꂼ‚ê‚ا‚ج‚و‚¤‚ب’·ڈٹ/’Zڈٹ‚ھ‚ ‚é‚ج‚¾‚낤‚©پB‚ـ‚½پA‚»‚ج‘I‘ً‚ھپAƒVƒXƒeƒ€‚جƒpƒtƒHپ[ƒ}ƒ“ƒX‚âƒ`ƒbƒv‚جƒRƒXƒgپAƒeƒXƒ^ƒrƒٹƒeƒB‚ب‚ا‚ة‚ا‚ج‚و‚¤‚ب‰e‹؟‚ً‹y‚ع‚·‚ج‚¾‚낤‚©پBژ©‚ç‚جگفŒv‚ةچإ“K‚ب‚à‚ج‚ھ‚ا‚ê‚إ‚ ‚é‚ج‚©‚ً’m‚é‚ة‚حپASoC‚ة‚¨‚¯‚éٹeNVM‚ج‰آ—pگ«‚ئƒgƒŒپ[ƒhƒIƒt‚ة‚آ‚¢‚ؤ’m‚ء‚ؤ‚¨‚©‚ب‚¯‚ê‚خ‚ب‚ç‚ب‚¢پiٹeژيNVM‹Zڈp‚ة‚آ‚¢‚ؤ‚حپA•تŒf‹Lژ–پw‚³‚ـ‚´‚ـ‚بNVM‹Zڈpپx‚ًژQڈئ‚³‚ꂽ‚¢پjپB

NVM‚ج“K—pŒآڈٹ

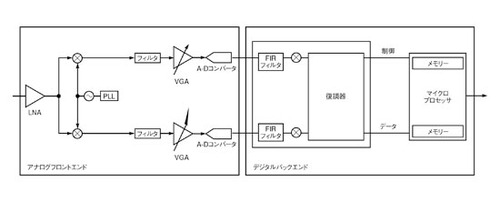

پ@‚±‚±‚إ‚حٹeژيNVM‚ً”نٹr‚·‚邽‚ك‚ةپARFژَگMƒVƒXƒeƒ€‚ً—ل‚ئ‚µ‚ؤژو‚èڈم‚°‚éپiگ}1پjپBڈ‚µچl‚¦‚½‚¾‚¯‚إ‚àپA‘g‚فچ‚فNVM‚ج‚¢‚‚آ‚©‚ج—ک—p•û–@‚ھ•‚‚©‚ٌ‚إ‚‚邾‚낤پB

پ@ƒAƒiƒچƒOƒtƒچƒ“ƒgƒGƒ“ƒh‚إ‚حپAƒAƒiƒچƒOگMچ†‚ھLNAپi’لƒmƒCƒYƒAƒ“ƒvپj‚ة“ü‚èپA‘±‚¢‚ؤƒ~ƒLƒTپ[پAƒtƒBƒ‹ƒ^پAA-DƒRƒ“ƒoپ[ƒ^‚ض‚ئگi‚قپBˆê•ûپAƒfƒWƒ^ƒ‹ƒoƒbƒNƒGƒ“ƒh‚إ‚حپAƒfپ[ƒ^‚ھƒ}ƒCƒNƒچƒvƒچƒZƒbƒT‚ة“’B‚·‚é‚ـ‚إ‚ةپAƒtƒBƒ‹ƒ^ƒٹƒ“ƒOپAƒ~ƒLƒVƒ“ƒOپA•œ’²‚ب‚ا‚جگMچ†ڈˆ—‚ھچs‚ي‚ê‚éپB‚±‚ج—ل‚إ‚حپAƒfƒWƒ^ƒ‹ƒoƒbƒNƒGƒ“ƒh‚ة‚¨‚¢‚ؤپA1‚آ‚جگMچ†ƒpƒX‚إگ§Œن‚ة‘خ‰‚µپA‚à‚¤1‚آ‚جگMچ†ƒpƒX‚إƒfپ[ƒ^‚ًˆµ‚¤‚à‚ج‚ئ‚µ‚و‚¤پBƒ}ƒCƒNƒچƒvƒچƒZƒbƒT‚حپAƒAƒvƒٹƒPپ[ƒVƒ‡ƒ“‚إ•K—v‚ب‘€چى‚ًƒfپ[ƒ^‚ة‘خ‚µ‚ؤژ{‚µپAژں’i‚ة‘—‚邱‚ئ‚ئ‚·‚éپB

پ@‚±‚ج‚و‚¤‚بRFژَگMƒVƒXƒeƒ€‚ج‚ا‚±‚ةNVM‚ًژg‚¤‚ئپAƒpƒtƒHپ[ƒ}ƒ“ƒX‚ًŒüڈم‚³‚¹پAگفŒv‚ًٹب‘f‰»‚·‚邱‚ئ‚ھ‰آ”\‚ة‚ب‚邾‚낤‚©پB‚»‚ج‰آ”\گ«‚حژٹ‚é‚ئ‚±‚ë‚ة‚ ‚éپB—ل‚¦‚خپAƒAƒiƒچƒOƒtƒچƒ“ƒgƒGƒ“ƒh‚إڈ—ت‚جNVM‚ًژg‚¤‚±‚ئ‚إپALNA‚جƒQƒCƒ“’²گ®پAƒ~ƒLƒTپ[‚ة‚¨‚¯‚éƒgƒٹƒ€ڈˆ—پAPLLپiphase locked loopپj‚جƒtƒBƒ‹ƒ^’²گ®پAƒAƒiƒچƒOƒtƒBƒ‹ƒ^‚جŒWگ”•دچXپAƒQƒCƒ“‚ئˆت‘ٹ‚ج’²گ®پAA-DƒRƒ“ƒoپ[ƒ^‚جƒgƒٹƒ€‚ب‚اپA‚³‚ـ‚´‚ـ‚ب‚ئ‚±‚ë‚إگ¸“x‚ًٹm•غ‚·‚邱‚ئ‚ھ‚إ‚«‚éپB

پ@گ»‘¢ƒvƒچƒZƒX‚ھ•د‚ي‚ê‚خƒAƒiƒچƒOƒRƒ“ƒ|پ[ƒlƒ“ƒg‚ج“ءگ«‚à•د‰»‚·‚éپB‚»‚ê‚ة‘خ‚µپANVM‚ً—ک—p‚µ‚ؤƒpƒ‰ƒپپ[ƒ^‚ً•دچX‚إ‚«‚é‚و‚¤‚ة‚µ‚ؤ‚¨‚¯‚خپA‰ٌکH‚ًڈي‚ة“Kگط‚ة“®چى‚³‚¹‚邱‚ئ‚ھ‚إ‚«‚éپB‚ـ‚½پA‰·“x‚ج•د‰»‚àƒAƒiƒچƒO‰ٌکH‚ج“®چى‚ة‰e‹؟‚ً‹y‚ع‚·پB‚±‚ê‚ة‚آ‚¢‚ؤ‚àپA‰·“x•د‰»‚جŒƒ‚µ‚¢ڈًŒڈ‰؛‚إ‚حپAMTPپimultiple times programmableپF‰½“x‚إ‚àڈ‘‚«چ‚ف‚ھ‚إ‚«‚éپj‚جNVM‚âپAOTPپione time programmableپFˆê“x‚¾‚¯ڈ‘‚«چ‚ف‚ھ‚إ‚«‚éپj‚جNVM‚ًƒxپ[ƒX‚ئ‚µ‚½ƒpƒ‰ƒپپ[ƒ^‚جƒ‹ƒbƒNƒAƒbƒvƒeپ[ƒuƒ‹‚ً’ا‰ء‚·‚邱‚ئ‚إپAƒVƒXƒeƒ€‚جگ¸“x‚ًˆغژ‚إ‚«‚و‚¤پB

پ@ƒfƒWƒ^ƒ‹ƒoƒbƒNƒGƒ“ƒh‚إ‚حپAƒoƒX•‚ھچL‚¢‚ظ‚اپA•K—v‚ئ‚ب‚éNVM‚ج—e—ت‚ح‘ه‚«‚‚ب‚é‚ح‚¸‚¾پB—ل‚¦‚خپADSPƒuƒچƒbƒN‚ة‚حƒtƒBƒ‹ƒ^ŒWگ”‚â•œ’²ƒpƒ‰ƒپپ[ƒ^—p‚ج‹L‰¯—جˆو‚ھ•K—v‚©‚à‚µ‚ê‚ب‚¢پBƒfپ[ƒ^‚ھƒ}ƒCƒNƒچƒvƒچƒZƒbƒT‚ة“’B‚µ‚½‚çپA•p”ة‚ة•دچX‚³‚ê‚éƒLپ[‚ًژg‚ء‚½•œچ†‰»‚âپAƒtƒŒپ[ƒ€‚ج“¯ٹْ‰»پA‚ ‚é‚¢‚حڈ¬‹K–ح‚بƒRپ[ƒh‚ًچXگV‚µ‚ؤ‚»‚ê‚ًٹi”[‚·‚é‚ئ‚¢‚ء‚½‚±‚ئ‚ھ•K—v‚ئ‚ب‚é‚©‚à‚µ‚ê‚ب‚¢پB‚±‚¤‚µ‚½ƒfپ[ƒ^ٹضکA‚ج—vŒڈ‚حپAƒfپ[ƒ^‚ھ‚¢‚آپA‚ا‚ج‚و‚¤‚ةچXگV‚³‚ê‚é‚ج‚©‚ئ‚¢‚¤‚±‚ئ‚ئپA‚»‚جƒTƒCƒY‚âچXگV‚ج——R‚ة‚و‚ء‚ؤ‚à•د‚ي‚ء‚ؤ‚‚éپB

پ@•\1‚ةپA‚±‚جRFژَگMƒVƒXƒeƒ€‚ة‚¨‚¯‚éƒpƒ‰ƒپپ[ƒ^‚ئNVM‚ة‹پ‚ك‚ç‚ê‚é—vŒڈ‚ب‚ا‚ً‚ـ‚ئ‚ك‚½پB

‚³‚ـ‚´‚ـ‚بNVM‹Zڈp

پ@‘g‚فچ‚فNVM‚ً—ک—p‚·‚éڈêچ‡پAگفŒvژز‚حپA’تڈي‚جCMOSƒvƒچƒZƒX‚ة‚ا‚ꂾ‚¯‚جƒ}ƒXƒNƒXƒeƒbƒv‚ً’ا‰ء‚µ‚ب‚‚ؤ‚ح‚ب‚ç‚ب‚¢‚©‚ً•]‰؟‚·‚éپBƒچƒWƒbƒNNVM‚ج‚و‚¤‚ة’ا‰ءƒ}ƒXƒN‚ھ•s—v‚ج‚à‚ج‚à‚ ‚ê‚خپASONOSƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹپ[‚ج‚و‚¤‚ة2پ`4–‡‚ج’ا‰ءƒ}ƒXƒN‚ً•K—v‚ئ‚·‚é‚à‚جپAƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹپ[‚ج‚و‚¤‚ة2پ`10–‡‚ج’ا‰ءƒ}ƒXƒN‚ً•K—v‚ئ‚·‚é‚à‚ج‚à‚ ‚éپiƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹپ[‚ة‚ح’تڈي2‘w‚جƒ|ƒٹƒVƒٹƒRƒ“‚ھ•K—v‚إ‚ ‚èپA3‚آ–ع‚جƒ|ƒٹƒVƒٹƒRƒ“‘w‚ھ•K—v‚ئ‚³‚ê‚éڈêچ‡‚à‚ ‚éپjپB‚ا‚ê‚ً‘I‘ً‚·‚é‚©‚حگفŒvژزژں‘و‚¾پB

پ@ƒVƒٹƒTƒCƒhŒn‚جƒqƒ…پ[ƒY‚ًژg‚¤NVM‚إ‚حپA‹L‰¯‘fژq‚ئ‚µ‚ؤƒ|ƒٹƒŒƒWƒXƒ^‚ھژg‚ي‚ê‚éپBگفŒvژز‚ھƒfƒoƒCƒX‚ًƒvƒچƒOƒ‰ƒ€‚·‚éچغ‚ة–ٌ10mA‚ج“d—¬‚ً—¬‚·‚±‚ئ‚إپAƒVƒٹƒTƒCƒh‚جژ©Œب‰ء”M‚ئƒGƒŒƒNƒgƒچƒ}ƒCƒOƒŒپ[ƒVƒ‡ƒ“‚ھ”گ¶‚µپAƒtƒBپ[ƒ‹ƒhژ_‰»–Œڈم‚إƒ|ƒٹƒqƒ…پ[ƒY‚ج•”•ھ‚ج’ïچR‚ھ‘ه‚«‚‚ب‚éپB’l‚ً“ا‚فڈo‚·چغ‚ة‚حMOS FET‚ًƒIƒ“‚ة‚µپAƒZƒ“ƒXƒAƒ“ƒv‚ھ‚»‚جڈَ‘ش‚ًŒںڈo‚·‚éپBƒqƒ…پ[ƒY•”•ھ‚ج’ïچR’l‚ج‘‰ء‚ة‚و‚èپA‹L‰¯‘fژq‚جڈَ‘ش•د‰»‚ھ”»•ت‚³‚ê‚éژd‘g‚ف‚¾پBƒqƒ…پ[ƒY‰ٌکH‚ة‚حˆê“x‚µ‚©ƒvƒچƒOƒ‰ƒ~ƒ“ƒO‚إ‚«‚ب‚¢‚ئ‚¢‚¤گ§–ٌ‚ھ‚ ‚邵پAƒvƒچƒOƒ‰ƒ~ƒ“ƒO‚ة—v‚·‚é“d—¬‚ھ‘ه‚«‚¢‚½‚ك”نٹr“I‘ه‚«‚بƒZƒ‹‚ھ•K—v‚ئ‚ب‚èپA‚ـ‚½گM—ٹگ«‚ج–ت‚إ‚ج–â‘è‚à‹N‚±‚蓾‚éپB

پ@‹L‰¯‘fژq‚ئ‚µ‚ؤپAƒIƒLƒTƒCƒhƒRƒ“ƒfƒ“ƒT‚ھژg‚ي‚ê‚éNVM‚à‚ ‚éپB‚±‚جƒ^ƒCƒv‚ج‚à‚ج‚إ‚حپAƒvƒچƒOƒ‰ƒ~ƒ“ƒO‚جچغپAƒXƒgƒŒƒXƒmپ[ƒh‚ة‘ه‚«‚ب“dˆ³‚ًˆَ‰ء‚·‚é‚ئژ_‰»–Œ‚ھ”j‰َ‚³‚ê‚ؤ‚µ‚ـ‚¤‚ئ‚¢‚¤–â‘è‚ھ‚ ‚éپB

پ@‘ه”¼‚جEEPROM‚ئƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹپ[‚ة‚حپAƒtƒچپ[ƒeƒBƒ“ƒOƒQپ[ƒg‹Zڈp‚ھ—ک—p‚³‚ê‚ؤ‚¢‚éپBƒtƒچپ[ƒeƒBƒ“ƒOƒQپ[ƒg‚جƒgƒ‰ƒ“ƒWƒXƒ^‚حپA‰×“d‚µ‚ؤ‚¢‚ب‚¢ڈَ‘ش‚إگ»‘¢‚³‚ê‚é‚©پAژ‡ٹOگü‚ً—p‚¢‚ؤ“d‰×‚ًڈء‹ژ‚µ‚½ڈم‚إژg—p‚·‚éپB‚±‚جƒtƒچپ[ƒeƒBƒ“ƒOƒQپ[ƒg‚جƒgƒ‰ƒ“ƒWƒXƒ^‚حپAƒzƒbƒgƒLƒƒƒٹƒA‚ج’چ“ü‚ة‚و‚èƒIƒ“‚ة‚ب‚éپB

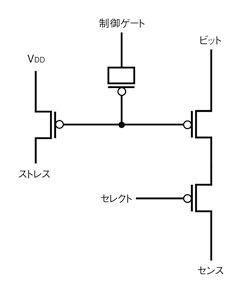

پ@MTP‚جƒچƒWƒbƒNNVM‚إ‚àپAƒtƒچپ[ƒeƒBƒ“ƒOƒQپ[ƒg‹Zڈp‚ً—ک—p‚·‚éپBƒ}ƒXƒN‚âƒvƒچƒZƒXƒXƒeƒbƒv‚ً’ا‰ء‚·‚邱‚ئ‚ب‚پA•Wڈ€“I‚بCMOSƒvƒچƒZƒX‚إƒZƒ‹‚ًژہ‘•‚إ‚«‚é“_‚ھچإ‘ه‚ج“ء’¥‚¾پiگ}AپjپBƒvƒچƒOƒ‰ƒ~ƒ“ƒOژ‚ة‚حپAگ§ŒنƒQپ[ƒg‚ًƒOƒ‰ƒEƒ“ƒh“dˆت‚إ•غژ‚µ‚½‚ـ‚ـƒgƒ“ƒlƒ‹ƒgƒ‰ƒ“ƒWƒXƒ^‚جƒQپ[ƒg‚ًچ‚“dˆت‚ةˆّ‚«ڈم‚°‚邱‚ئ‚إFNپiFowler-Nordheimپjƒgƒ“ƒlƒٹƒ“ƒO‚ھ”گ¶‚µپAƒtƒچپ[ƒeƒBƒ“ƒOƒQپ[ƒg‚ج“d‰×‚ھڈء‹ژ‚³‚ê‚éپBگ§ŒنƒQپ[ƒg‚ًچ‚“dˆت‚ةˆّ‚«ڈم‚°پAژc‚è‚جƒmپ[ƒh‚ًƒOƒ‰ƒEƒ“ƒh“dˆت‚إ•غژ‚·‚ê‚خپAFNƒgƒ“ƒlƒٹƒ“ƒO‚ً‹t•ûŒü‚ة“‚©‚¹‚邱‚ئ‚ة‚ب‚èپAƒQپ[ƒg‚ة“d‰×‚ھƒ`ƒƒپ[ƒW‚³‚ê‚éپBƒXƒgƒŒƒXƒmپ[ƒh‚©‚ç‚جƒzƒbƒgƒLƒƒƒٹƒA’چ“ü‚ة‚و‚ء‚ؤƒZƒ‹‚ًƒvƒچƒOƒ‰ƒ€‚·‚邱‚ئ‚à‰آ”\‚إ‚ ‚éپB

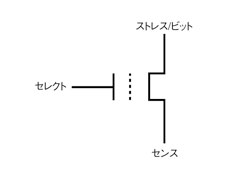

پ@‘g‚فچ‚فEEPROM/ƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹپ[‚إ‚حپA2ڈdƒ|ƒٹƒVƒٹƒRƒ“‚ًژg—p‚µ‚ؤƒtƒچپ[ƒeƒBƒ“ƒOƒQپ[ƒg‚ة“d‰×‚ً’~گد‚·‚éژd‘g‚ف‚ھ—p‚¢‚ç‚ê‚éپiگ}BپjپBƒvƒچƒOƒ‰ƒ~ƒ“ƒO‚جچغ‚ة‚حپAƒXƒgƒŒƒX/ƒrƒbƒgƒmپ[ƒh‚ًچ‚“dˆت‚ةˆّ‚«ڈم‚°پAƒZƒŒƒNƒgƒmپ[ƒh‚ًƒOƒ‰ƒEƒ“ƒh“dˆت‚ـ‚½‚ح•‰‚ج“dˆت‚ئ‚·‚邱‚ئ‚إFNƒgƒ“ƒlƒٹƒ“ƒO‚ً”گ¶‚³‚¹‚éپB‚±‚ê‚ة‚و‚èپAƒtƒچپ[ƒeƒBƒ“ƒOƒQپ[ƒg‚ج“d‰×‚ًڈء‹ژ‚·‚éپBƒZƒŒƒNƒgƒmپ[ƒh‚ًچ‚“dˆت‚ةˆّ‚«ڈم‚°پAژc‚è‚جƒmپ[ƒh‚ًƒOƒ‰ƒEƒ“ƒh‚إ•غژ‚µ‚ؤFNƒgƒ“ƒlƒٹƒ“ƒO‚ً‹t•ûŒü‚ةچى—p‚³‚¹‚ê‚خپAƒtƒچپ[ƒeƒBƒ“ƒOƒQپ[ƒg‚ة“d‰×‚ھ’چ“ü‚³‚ê‚éپBƒXƒgƒŒƒX/ƒrƒbƒgƒmپ[ƒh‚©‚ç‚جƒzƒbƒgƒLƒƒƒٹƒA’چ“ü‚ة‚و‚ء‚ؤ‚àƒZƒ‹‚ًƒvƒچƒOƒ‰ƒ€‚إ‚«‚éپB

پ@SONOSƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹپ[‚àƒtƒچپ[ƒeƒBƒ“ƒOƒQپ[ƒg‚ً—ک—p‚·‚éƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹپ[‚ئ“¯‚¶‚و‚¤‚ب•û–@‚إ“®چى‚·‚éپB‚½‚¾‚µپA“d‰×‚ج’~گد‚ة‚حƒtƒچپ[ƒeƒBƒ“ƒOƒQپ[ƒg‚ج‘م‚ي‚è‚ة’‚‰»•¨‚ج‘w‚ھژg—p‚³‚ê‚éپBˆê”ت‚ةپASONOS‚حƒtƒچپ[ƒeƒBƒ“ƒOƒQپ[ƒg‚ً—ک—p‚µ‚½NVM‚و‚è‚à’ل‚¢“dˆ³‚إƒvƒچƒOƒ‰ƒ~ƒ“ƒO/ڈء‹ژ‚ھچs‚¦‚éپBƒtƒچپ[ƒeƒBƒ“ƒOƒQپ[ƒg‚ً—p‚¢‚½NVM‚جگ»‘¢‚ة‚حپA6پ`10‚جƒ}ƒXƒN’ا‰ء‚ھ”گ¶‚·‚é‚ھپASONOSƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹپ[‚إ‚ح’تڈي‚جCMOSƒvƒچƒZƒX‚ة2پ`3‚جƒ}ƒXƒN’ا‰ء‚ًچs‚¤‚¾‚¯‚إچد‚قپB

Copyright © ITmedia, Inc. All Rights Reserved.