マルチコア時代の牽引役は最新メモリーアクセス技術:Microprocessor Forum 2007特別リポート(3/3 ページ)

2007年5月21日〜23日、米国サンノゼにおいて「Microprocessor Forum 2007」が開催された。フォーラム全体を通じて見えてきたのは、マルチコアプロセッサの普及が進む中、そのメリットを追求するために、各企業がメモリーアクセス技術にポイントを置いて開発を行っていることだ。

キャッシュの一貫性の保証

外部メモリーへのアクセスは非常に重要なことだが、マルチコアプロセッサにおいては、ほかにも解決すべき課題がある。それは、各プロセッサコアに独立したキャッシュメモリーが存在する場合に、キャッシュのコヒーレント(一貫性)を保つことだ。一方のプロセッサコアがキャッシュのデータを書き換えた場合に、その状態をもう一方のプロセッサコアが知らないまま同じアドレスにアクセスしてしまうと処理に矛盾が生じてしまうからである。

英ARM社は、この問題に対処するためのものとして「MPCore Snoop Control Unit(MSCU)」というハードウエアを紹介した。これはキャッシュ間のコヒーレントを保つためのもので、個々のプロセッサコアが備えるL1キャッシュメモリーと複数のプロセッサコアで共有されるL2キャッシュメモリーに、プロセッサコアから独立してアクセスできるようにするユニットである。あるプロセッサコアでキャッシュの書き換えが発生した際、MSCUは各キャッシュにアクセスしてデータの書き換えを行う。MSCUは、どのキャッシュメモリーにどのメモリーがコピーされているかを示すデータを保存しており、その情報を基にキャッシュメモリーのコヒーレントを保つ。

また、同社は個々のプロセッサコアが備えるMMU(memory management unit)のコヒーレントを保つハードウエアも提案している。この処理は、同社の従来のマルチコアプロセッサでは、2000サイクルに上るソフトウエア処理によって実現していた。この部分の効率化を図ることが可能になるという。

依然として低消費電力化も焦点

Microprocessor Forum 2007では、マルチコアプロセッサ以外にも興味深いテーマの講演が多数行われた。ここでは、低消費電力化を実現する技術をいくつか取り上げて紹介しておく。

■ドミノ回路で省電力化

米AMCC社は、POWERアーキテクチャを採用した低消費電力の32ビットプロセッサコア「Titan」についての講演を行った。Titanはアウトオブオーダー実行のプロセッサコアであり、4000DMIPS(動作速度は2GHz)の処理能力を備え、消費電力は2.5W(標準値)である。このように消費電力を削減できた理由は、米Intrinsity社の「Fast14」技術を用いたことだという。

Fast14は、nMOSとpMOSの両方を用いるスタティックCMOS論理回路をnMOSだけのダイナミック論理回路(ドミノ回路)に変換するものである。nMOSだけで論理回路を構成できる(チャージ用などにpMOSも必要)ため、トランジスタ数を削減できるので電力と面積を削減できる、ラッチ回路を必要しない、nMOSはpMOSに対して移動度が2〜3倍高いため高速化できるといったメリットが得られる。

ドミノ回路は、遅延制御が難しいこと、ノイズに弱いこと、チャージに時間を要することなどから、高速性を求められる用途以外にはほとんど使用されていない。Intrinsity社は、これらの問題を回避するために、90度ずつ位相をずらした4つのクロックを用い、クロックの遅延時間とチャージ時間を調整しやすくした。また、ノイズの問題に対しては、ステートマシンのワンホットエンコーディングのような変換によってデータを送る「1 of N Dynamic Logic(NDL)」技術を用いて対応している。NDLでは複数の信号線のうち、1本だけがハイレベルになり、周囲の線がグラウンドガードとして働く。そのため、ノイズ耐性を高めることができるという。

■High-kを用いずにリークを削減

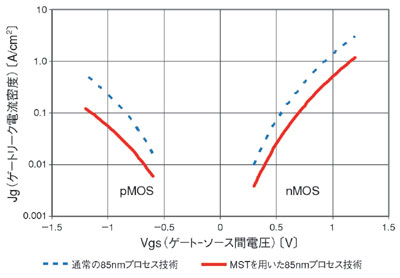

米MEARS Technologies社の「MST(MEARS silicon technology)」は、ゲート電極の下にスーパー格子構造と呼ばれる積層構造を形成し、縦方向と横方向のバンドギャップを操作するというものだ。これによって、ハフニウムなどのHigh-k材料を用いることなく、リーク電流を削減しつつ、ドライブ電流を増加させることが可能になるという。このMSTを85nmのプラズマ窒化酸化膜(PNO)を採用したCMOSプロセス技術に適用したところ、nMOSのリーク電流の60%、pMOSのリーク電流の80%が削減され、ドライブ電流が20%近く増加するという結果が得られている(図A)。

通常のプロセス技術では、ドライブ電流を増加させるために絶縁膜を薄くすると、リーク電流が増加する。それに対し、MSTはリーク電流/ドライブ電流ともにゲートの性能を向上させる方向に作用する。MEARS社社長兼CTO(最高技術責任者)のRobert J. Mears氏は、その理由を「バンドギャップが層状に構成されることで、電子が横方向に移動しやすく、縦方向に移動しにくくなるからだ」と説明した。

このMST技術を従来のプロセス技術に適用する場合には、工程を1つ追加するだけで済み、新たな製造装置や材料を必要としない。

Copyright © ITmedia, Inc. All Rights Reserved.