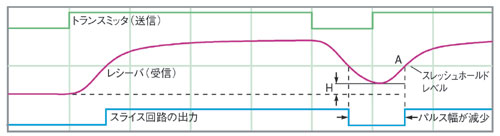

図1は、トランスミッタからレシーバに送られる信号の波形を表している。トランスミッタから送信された矩形パルス信号が同軸ケーブル内を長く伝搬すると、パルス信号に含まれる高周波成分が減衰してエッジが丸まる。その結果、レシーバで受信するパルス信号の立ち上がり/降下の傾斜は送信時に比較して緩やかになる。

レシーバが受ける信号が降下する部分に着目してみよう。受信パルスは、時間的な余裕がないため、ローレベルに降下し切る前に立ち上がり始めている。点Aに向かう立ち上がり波形は、本来よりも高さHだけ高いレベルからスタートすることになる。そのため、そのパルスのローの区間が所定のスレッシュホールドレベル以下にある時間が短くなる。つまり、レシーバ側のスレッシュホールドレベルである点Aに達するまでの期間が短くなる。この期間がどの程度短くなるかは伝送ラインの減衰特性から予測可能である。言い換えれば、この現象は実験の度に同じ結果をもたらす。

受信パルス信号をスライス回路で点Aのレベルによりスライス(2値化)すると、得られるパルスはトランシーバから送信されたものより幅が狭くなる。同様なパルス幅の減少は、TEM(transverse electromagnetic mode)伝送線路を構成要素とする、帯域幅が制限されたシステムのすべてに認められる。このようなシステムでは、高周波域の減衰により、ローまたはハイの状態が長く続いた後に来る短いパルスは、常にその幅が短くなるのだ。

以上のことから、スライス回路の出力パルス幅の減少の度合いが、伝送ラインの性能を評価する優れた指標になり得ることが分かる。実は、現在、筆者自身がこの手法に魅了されている。その理由は、最近の高速シリアルリンクの受信信号波形を実測することの難しさが身に染みているからだ。

その測定を困難にしている1つの要因は、多くの場合、信号配線がBGAのボールの下にあり、プローブを当てる場所がないということである。プリント基板の裏面にあるビアホールにであればプローブを当てることはできるが、そのビアが計測すべき信号の受信点から遠く離れていると、正確な測定は期待できない。

例として、6.25ギガビット/秒の高速シリアルリンクについて考えてみよう。この速度の信号パルスの場合、レシーバの受信点での立ち上がり/降下時間はおよそ100〜160ps程度になる。ここで、レシーバの入力容量により、入射信号振幅の20%の反射波が発生すると仮定しよう。この反射はレシーバの受信点での信号の立ち上がり/降下タイミングで生じ、これによりエッジに遅れが出るが、データの再生には影響しない。一方、受信点から0.25インチ(約6mm)だけ離れたビアについて考えると、このビアの位置で観測される反射は往復0.5インチの伝播時間に相当する90psだけ遅れて到着する(1インチ当たり180psの遅延を仮定)。つまり、入力容量による20%振幅の反射波をこのビアで観測すると、その位置は受信信号のアイパターン開口のほぼ中央部に来るということだ。これでは、波形の計測はお手上げである。

こうしたタイミング的な障害を避けるには、プローブの位置と受信点との距離を、パルスの立ち上がり/降下時間を踏まえて十分に短くしなければならない。それに加え、プローブが計測対象の信号に対して重い負荷にならないように選択する必要がある。これらの要求を満足するのは容易ではない。 それに対し、パルス幅の減少を観測する方法であれば、プローブを当てる位置やその負荷の制限を受けることがない。そしてその測定結果は、システムの帯域を評価する指標となり得る。加えて、この計測には、スライス回路を含む系全体の性能を評価することにもなるという利点がある。

<筆者紹介>

Howard Johnson

Howard Johnson氏はSignal Consultingの学術博士。Oxford大学などで、デジタルエンジニアを対象にしたテクニカルワークショップを頻繁に開催している。ご意見は次のアドレスまで。www.sigcon.comまたはhowie03@sigcon.com。

Copyright © ITmedia, Inc. All Rights Reserved.