民生機器向けSoCはどうあるべきなのか?:「ZEVIO」プロジェクトに見る1つの解(2/3 ページ)

民生電子機器向けの半導体ビジネスで成功するためには、必ずしも最速のSoCを最新かつ最高のプロセス技術で製造する必要があるというわけではない。このことを示唆する例を米LSI社の「ZEVIO」プロジェクトに見ることができる。

最適な製造プロセスを選ぶ

LSI社は、設計したチップを、90nmや65nmプロセスではなく、成熟した130nmローパワープロセスで製造することにした。それにより、チップコストを抑え、安定した電力管理を実現し、DFM(design for manufacturing)ツールの使用を避けることができるからだ。この選択が設計期間の短縮にもつながった。藤本氏は、「ZEVIOはシステム価格が100米ドル未満のアプリケーションをターゲットとする。高価なチップを作ることなら誰にでもできるが、特にブランド力のないビデオゲーム機器ベンダーなどは、製品に搭載されるチップのコストが上昇していることに悩まされていた」と語る。その上で、同氏は次のように指摘した。

「130nmのように成熟して安定したプロセスで製造しても、性能的に十分なチップができるのに、多くの企業は最新のプロセスへと移行しがちだ。成熟した技術というだけの理由で、130nmプロセスをもう採用しない企業がある。しかし、われわれは、巧みなエンジニアリングによってハイエンドの設計を実現することができると感じた。顧客は競合企業から、最新の用語がちりばめられた高性能な製品についてさまざまな話を聞くだろうが、最終的には予算の範囲内で最良のチップを得ることが重要だ。ZEVIOは成熟した130nmプロセス技術を使ったが、コストと性能の面で最適な選択だった」。

先述したように、LSI社は、ZEVIOをある特定用途に向けたASICではなく、再利用可能なプラットフォームにしたいと考えた。そのため、LSI社の製品群に加え、サードパーティ製のIPコアとも組み合わせが可能なIPコアを開発することに主眼を置いた。LSI社はIPベンダーであるコトと共同で、ZEVIOの3Dグラフィックスプロセッサのコアを開発した。藤本氏によると、コトのエンジニアのうち数名は、以前に任天堂のゲーム機器「ゲームボーイ」の設計チームの一員として開発に携わった経験があるという。それに対し、LSI社はこの分野における経験がほとんどなかった。「コトのエンジニアはソフトウエア開発者が要求する機能について、多くの知識を提供してくれた。また、そのノウハウの多くをハードウエアに適用することを支援してくれた」(藤本氏)という。

コトの設計チームがコアの仕様定義と検証のほとんどを担当し、LSI社の設計者らはコアの設計とRTL実装を担当した。16ビットの3Dグラフィックスプロセッサは30万ゲートしかなく、75MHz動作時の消費電力は20mWである。その処理能力は、1秒間に150万個のポリゴンの描画が可能なレベルであった。

16ビットI/Fでバスネックを解消

藤本氏によれば、ZEVIOで行う処理において潜在的にボトルネックとなるのは、メモリーコントローラおよび、そのコントローラとシステムメモリー間のインターフェースであったという。一般的に考えれば、目標の性能を達成する容易な方法は、32ビットのインターフェースを使ってデータを高速に転送することである。しかし、LSI社は、コストを低減するために16ビットインターフェースのメモリーで同程度の性能を得る方法を考案しなければならなかった。

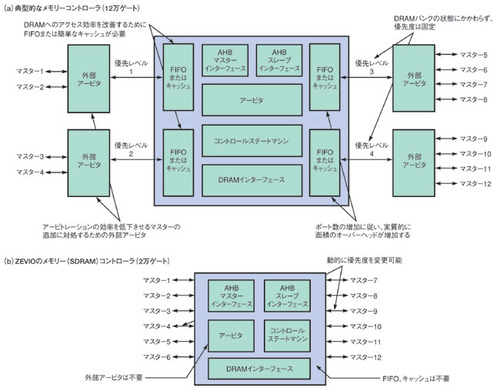

ZEVIOの設計チームは16ビットインターフェースを用いて、効率的なアービトレーション(同時に発生する複数の要求を調停する処理)を行う、効率的なコントローラを最初から設計する必要があった(図3)。「16ビットインターフェースを見て気が付いたのは、SDRAMに多くのコマンドを発行できる、適切なタイミングウィンドウを設定することが可能であるということだ」と藤本氏は述べた。同氏は、1バスクロックサイクルで2ワードを取得するコントローラ技術を採用することにした。藤本氏は「この技術を使えば、タイミングスロットを効率的に利用して、複数のバンクを解放することができる。この技術に関して特許申請を行っている」と藤本氏は述べ、この技術を同アーキテクチャにおける主要な革新の1つと見なしている。

ZEVIOの設計チームは、コントローラのRTLを記述し、PoF(proof of concept:概念の検証)シミュレーションを実施した。「典型的なメモリーコントローラの設計に対してかなりの改良を加えた。この段階で、われわれは16ビットインターフェースでも良い性能が得られることを実証した」と同氏は述べる。

ボトルネックの解消に関しては、関連するバスのプロトコルについても考察することが必要であった。ZEVIOの設計グループは、広く使用されているARM社のAMBA(advanced microcontroller bus architecture)AHB(AMBA high speed bus)プロトコルを使うことに決めた。しかし、同プロトコルのいくつかの非効率な部分を克服する方法を考案しなければならなかった。具体的には、ランダムアドレスへのバースト書き込みができないことと、十分に大きいバースト書き込みを指定することができないという課題を改善する必要があった。これらの問題に対処するため、設計グループはAMBA AHBに独自の拡張を加え、メモリーコントローラの効率を2倍に改善した。

仕様定義の段階での問題を解決した後、10〜15人の設計/検証エンジニアで構成されていた設計グループは、RTL設計に着手した。その際には、「メモリーコントローラ、グラフィックスプロセッサコア、サウンドプロセッサの各IPコアおよび全体的な統合を担当するチームにそれぞれ分割した」(藤本氏)という。

Copyright © ITmedia, Inc. All Rights Reserved.