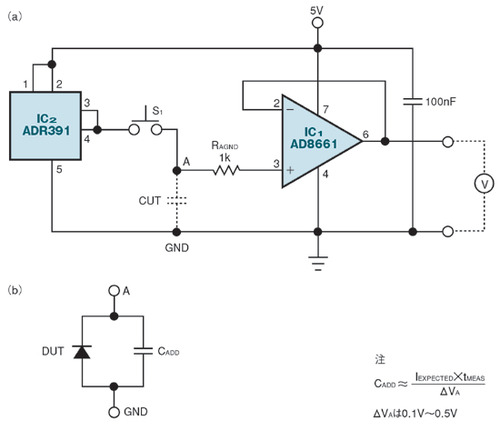

図1(a)に示す回路は、ボルテージフォロワを構成するオペアンプIC1と基準電圧源のIC2から構成されている。IC1は米Analog Devices社のオペアンプ「AD8661」で*1)、IC2は同社の高精度基準電圧源「ADR391」である*2)。IC1は、入力バイアス電流の最大値が1pA(標準値は0.3pA)であり、入力オフセット電圧の最大値が100μV以下(標準値は30μV)である。このような特性であるため、このオペアンプは、ほとんどの種類のコンデンサにおける自己放電電流の計測に使用できる。例えば、タンタルコンデンサやフィルムコンデンサのリーク電流は、IC1の入力バイアス電流より相当に大きい。

図1の回路による計測のフローは以下のようになる。まず初めに、測定の対象とするコンデンサ(CUT:capacitor under test)を、スイッチS1を介してIC2の出力に接続し、基準電圧レベルの2.5Vまで充電する。しばらく間をおいてから、スイッチS1を開放して基準電圧源との接続を切り離す。切り離してから一定の時間が経過した後に、IC1の出力電圧をデジタル電圧計によって計測する。計測までの経過時間は、出力電圧が初期電圧から0.1〜0.5V(ΔVO)程度低下するまでの時間に定める。この計測結果からリーク電流IOは、C×ΔVO/tMEASによって求められる。ここで、CはCUTの容量、tMEASはΔVO分だけ電圧が低下するまでにかかる時間である。

図1の回路は逆バイアス時のダイオード、あるいはオフ状態の各種半導体スイッチング素子(JFET、MOS FET、BJT、SCR、IGBTなど)のリーク電流の計測にも利用できる。その場合、前記のCUTの部分を、計測の対象とするデバイス(DUT:device under test)とコンデンサCADDで置き換える(図1(b))。計測のフローは上述したのと同様であり、計算にも同様の式IO=C×ΔVO/tMEASを用いる。ただし、この場合のCはCADDの容量になる。低電力用のDUTに対しては、ほとんどの場合、CADDとして10nFのポリエチレンフィルムコンデンサを使用することができる。高電力用のデバイスの場合、CADDは、電圧を印加しないときのDUTの浮遊容量の少なくとも10倍以上大きい値にする必要がある。

図1(b)の手法を利用すれば、数10MΩから2TΩほどの超高抵抗の計測も可能である。その場合、前記リーク電流の計算式IO=C×ΔVO/tMEASにおけるIOが、基準電圧の印加時に抵抗を流れる電流値になる。このことから概略の抵抗値が次式のように計算できる。

より正確には、以下の式となる。

各計測において注意すべき点は、出力電圧の低下量が基準電圧の1/5を超えないようにし、厳密には指数関数的な変化である出力電圧の変化を線形変化に近似できるようにすることだ。また、図1(a)で使用しているスイッチS1は、リーク電流が1pA以下のものであることが必要となる。このような低リーク電流のスイッチとしては、端子が金メッキ/燐青銅タイプのものが適切だ。コネクタにも、金メッキ端子を用いた高級品を使用する必要がある。また、CUT/DUTの接続にも、コネクタと同様に金メッキされたクリップを用いる。回路自体のリーク電流を最小にするために、プリント配線板は使用しない。

図1 リーク電流の計測回路 初めにスイッチS1を閉じてCUTに基準電圧を印加する(a)。続いてS1をオープンした状態でボルテージフォロワ回路の出力の時間に対する変化を計測する。半導体デバイスのリーク電流を計測するには、CUTの部分をDUTとCADDに置き換える(b)。

脚注

※1…AD8661 16V Low Cost, High Performance CMOS Rail-to-Rail Operational Amplifiers.

※2…ADR391 2.5V Micropower, Low Noise Precision Voltage References with Shutdown.

Copyright © ITmedia, Inc. All Rights Reserved.