オペアンプの新・SPICEマクロモデル:データシートの値に基づくシミュレーションが可能に(2/3 ページ)

本稿では、SPICEシミュレーションで用いるオペアンプのマクロモデルを紹介する。これを利用すれば、製品のデータシートに記載されたパラメータの値を用いて、新たに使用するオペアンプでもモデルを容易に作成できる。

マクロモデルの詳細

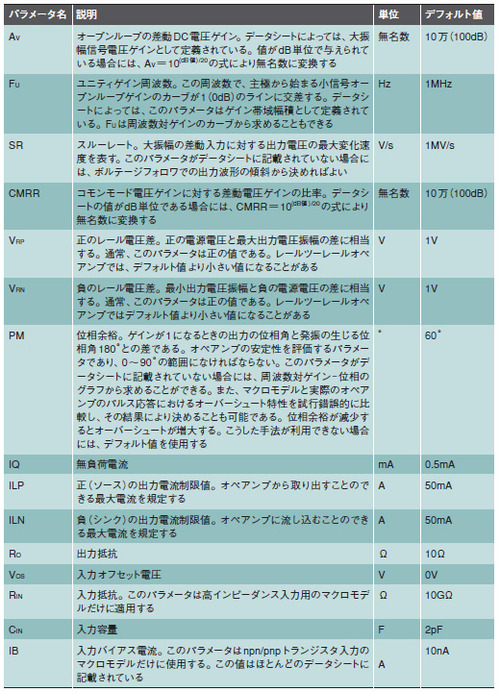

マクロモデルの動作特性は、上述した各数学関数ブロックのパラメータによって決まる。表1に示したのが、本マクロモデルで使用しているモデルパラメータの一覧である。以下、主なパラメータの概要を説明する。

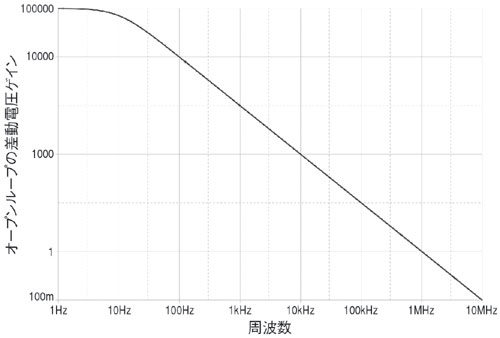

パラメータAVは、オープンループにおける入出力間の差動DC電圧ゲインを表す。パラメータFUは、ユニティゲイン周波数であり、これにより入力段のトランスコンダクタンスが設定され、小信号時のAC特性を表現する。図3に示したのは、AVを10万、FUを1MHzとした場合の本マクロモデルの周波数特性である。

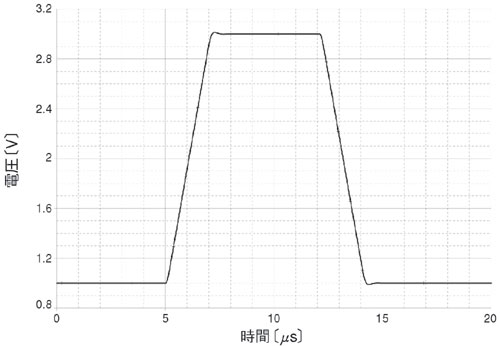

パラメータSR(slew rate:スルーレート)は、位相補償容量CCの最大充電速度を制限する制限関数を使用して最大スルーレートをモデル化するのに用いる。図4は、マクロモデルを用いて構成したボルテージフォロワ回路で、最大スルーレートが1MV/sの場合のパルス応答を表す。

パラメータCMRR(common mode rejection ratio:同相信号除去比)は、DCにおけるコモンモードゲインと差動ゲインの相対比の設定に用いる。

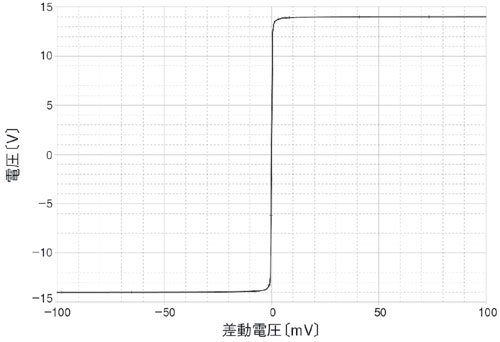

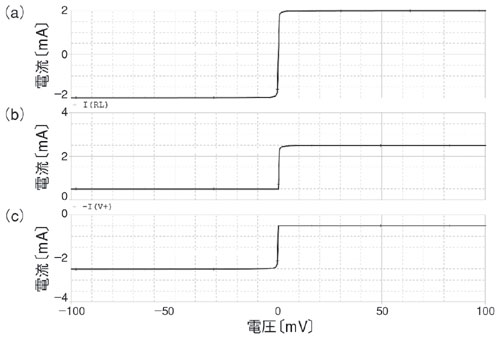

パラメータVRP(正のレール電圧)とVRN(負のレール電圧)は出力電圧振幅を決める。図5は、AVを10万、VRPとVRNをそれぞれ1V、電源電圧を±15Vとした場合の差動入力に対するDC応答である。

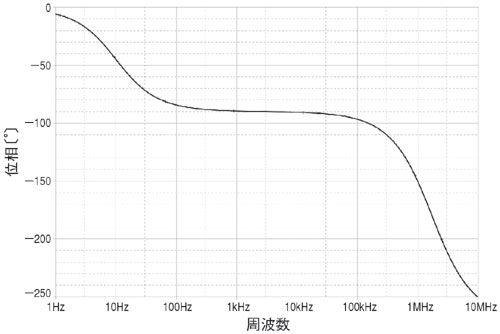

オペアンプの安定性を評価するには、位相余裕(phase margin)を使用するのがよい。位相余裕はユニティゲイン周波数における発振のしやすさの程度を表す。本マクロモデルでは、パラメータPMが位相余裕に対応する。位相余裕は高次極の周波数に依存し、マクロモデルでは、GP1、GP2、EP1、RP1、RP2、CP1、CP2を使用して高周波域に2つの高次極を配置している。容量パラメータであるCP1とCP2は、この極の周波数とパラメータPMを関連付ける。図6は、ユニティゲイン周波数(FU)を1MHz、周波数FUでの位相余裕(PM)を30°とした場合のマクロモデルの位相応答である。マクロモデルのパラメータPMを調整すれば、パルス応答のオーバーシュート特性を実際のオペアンプ特性に近づけることができる。

ほとんどのオペアンプの無負荷電流(quiescent current:無信号、無負荷時の消費電流)は、電源電圧にはあまり依存しない。マクロモデルの無負荷電流はXIQ(サブサーキットILOADBに対応)によって規定される。サブサーキットILOADBは、SPICEのJFETモデルを使用したもので、電圧が印加された場合にのみ動作する定電流負荷を表現する。無負荷電流値は、パラメータIQによって決まる。電圧源ABM2は正負の供給電源電圧の中心点に基準電圧VRを与える。マクロモデルでは入力信号の基準レベルとしてグラウンドレベルではなくこのVRを使う。ノードVRの電圧レベルは、そのノードに流れ込む、あるいは流れ出る電流によって変化することはない。

マクロモデルで使用する関数の中には出力電流に依存するものがある。電流制御電圧源HOはマクロモデルの出力電流値を規定し、HOに接続されるEI+とEI−がIOP、IONを決定する。IOPはマクロモデルの正電流(ソース)に対応し、IONは負電流(シンク)に対応する。GI+とGI−は出力電流が正負電源のそれぞれから供給されることをモデル化するもので、各電源からの負荷電流をIOP、IONによって決める。図7は、IQを0.5mAとした場合について、マクロモデルの出力電流と電源電流をプロットしたものである。

オペアンプの出力段では出力電流が決まるが、その電流値の決まり方は正(ソース)と負(シンク)の出力電流では異なることが多い。このような出力電流をモデル化するために、EIL+とEIL−が正負の出力電流をパラメータILP、ILNの決める値に制限するようにしている。EIL+とEIL−は、出力電流がILPまたはILNを超過しない限りは出力電圧の値に影響しない。出力電流の超過が生じた場合には、電流の極性に応じてEIL+またはEIL−が出力電圧を減少させ、出力電流をILPまたはILNが決める値に制限する。

抵抗パラメータのROはマクロモデルの出力抵抗を表す。電圧源パラメータのVOSは入力オフセット電圧を表す。R1、R2、C1、C2はパラメータRINとCINとともに入力抵抗と入力容量を規定する。図1に示した簡略化した入力抵抗モデルは、高インピーダンス入力、特にFET入力のオペアンプのモデル化には適しているが、npn/pnpトランジスタ入力の入力電流に対しては適切なモデルではない。

この問題の解決策が図2に示す入力段のモデルである。図2(a)に示したOPAMPMODNの入力段モデルでは、npnトランジスタのベース‐エミッタ接合をダイオードD1とD2によりモデル化している。XIBはサブサーキットILOADBを使用しており、パラメータIBはnpnトランジスタ入力のオペアンプの入力バイアス電流に対応している。実際のオペアンプでは、入力が正常動作範囲内にあって、入力トランジスタが両方とも逆バイアス状態になると、入力バイアス電流がゼロになり、オペアンプがオフになる。マクロモデルでは、この特性を入力段のABM3I2によってモデル化している。ABM3I2はHIBを経由して入力バイアス電流を検出する。そして入力バイアス電流がゼロになった場合に、ABM3I2のリミット関数が作用して出力電流をゼロにする。図2(b)に示すマクロモデルの入力段はサブサーキットOPAMPMODPで定義されており、pnpトランジスタ入力の入力段をモデル化する。

Copyright © ITmedia, Inc. All Rights Reserved.