インターフェースIC活用のススメ:その意義、各種方式の特徴、使いどころを探る(1/4 ページ)

ロジックICの電源電圧の低下に伴い、インターフェースICの重要性が増してきた。現在では、単なる負荷駆動の手段ではなく、より効率が良く、より安全な信号伝送の手段としてその価値は高まってきている。本稿では、まずインターフェース回路の基本を再確認した上で、各種インターフェースICの果たす役割や最新の製品動向を紹介する。

インターフェースICの重要性

ロジック信号の伝送方式は、15VのCMOS 4000シリーズから、5VのTTL(transistor to transistor logic)へと移り変わった。その後、電圧は下がり続け、最近では3.3V、2.7V、1.8VのCMOSレベルまで低下した。最先端のプロセスでは、1V以下で動作するデジタルロジックを用いるのが一般的である。しかし、このロジック電圧では、ソレノイドやツイストペアケーブル、パワーICなどを駆動することはできないので、最先端プロセスを用いたICには、外付けのインターフェース回路が必要となる。従って、設計者は、MOS FETのドライバやオープンコレクタソレノイドドライバ、LVDS(low voltage differential signaling:低電圧差動伝送)、絶縁ドライバなど、広い範囲にわたる手法を理解しておく必要がある。

回路間のインターフェースには、異なる電圧レベルや異なるインピーダンスの信号を接続しなければならないという難しさがある。また、例えば、CE(Conformite Europeenne)の試験に合格しようと試みた経験のある人ならば、現実世界に存在するデバイスや信号は電圧サージやスパイクにさらされており、その問題に対処しなければならないことを知っているだろう。これらの問題に加え、多くの最新インターフェースICは高い周波数で動作しており、そのことによって、さらなる問題が生じることもある。

トランジスタによるインターフェース

通常、LEDをドライブする際にはトランジスタを用いる。これが最も簡単なインターフェース回路の例である。ここでは、まずトランジスタによるインターフェース回路について解説する。

・バイポーラトランジスタ

まず最も基本的なデバイスの1つであるバイポーラトランジスタを取り上げる。これを通して、インターフェースの問題を見ていく。

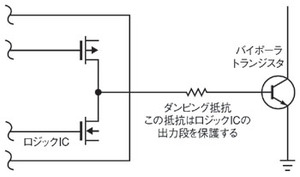

バイポーラトランジスタは0.6Vほどのベース電圧があれば動作するので、原理的には大部分のロジックICによってバイポーラトランジスタを駆動することができる。接続の1つの方法は、ロジックICからの出力に抵抗(ダンピング抵抗)を挿入してトランジスタのベースに入力するというものである(図1)。バイポーラトランジスタをロジックICで直接駆動することもできるが、ロジックICの内部抵抗によってバイポーラトランジスタへのベース電流を制限するのは良い方法ではない。なぜなら、バイポーラトランジスタをオンの状態にすると、そのベースは0.6Vに保たれるため、ロジックICの出力がショートの状態になってしまうからだ。このように、トランジスタをロジックICの出力に接続するという単純な作業にさえも知識/工夫を要するということである。

以下に、設計者がすべきことを順を追って説明する。まず、回路が動作する温度におけるバイポーラトランジスタのβ(電流増幅率)を調べる。次に、その値を用いて、負荷が最も大きい状態でバイポーラトランジスタをオンにするために必要となるベース電流値を求める。負荷電流は温度によって変化することも覚えておいてほしい。そして、使用しているロジック部品のデータシートのグラフを参照する。ここでも、実際の駆動電流を得るために、温度を考慮する必要があるだろう。

駆動電流は電圧降下に依存する。バイポーラトランジスタはベース電圧が0.6V以上の条件で動作するが、CMOSのロジックICは電源電圧レベルを出力し、バイポーラのロジックICの場合は電源電圧よりも0.6V、またはダイオードの降下電圧相当分だけ低い電圧を出力する。トランジスタが必要とする電圧と電流を知ることによリ、抵抗の値を算出することができる。例えば、トランジスタが完全にオンの状態になるように、計算上の必要な抵抗値が150Ωであるなら、実際には75Ωへと半分にすることが望ましい。次にロジックICが消費する電力を調べ、消費電力の仕様を超えていないことを確認する。例えば8出力のロジックICの場合、8つの出力バッファに負荷を接続すると、TSSOPなどの熱を拡散しにくい小さなパッケージでは、部品が焼損してしまう恐れがある。また、ロジックICではそれぞれ消費電力に対する温度ディレーティングが決まっているため、部品に過度のストレスをかけないようにその値を考慮することが必要だ。

もう1つ注意すべきことがある。それは、抵抗の値が低すぎたり、抵抗を完全になくしてしまったりすると、トランジスタを過飽和状態で駆動することになり、オフ状態になるまでの時間が長くなるということだ。この現象は、ベース‐エミッタ接合に注入した余分な正孔/電子がすべて再結合しなければコレクタ‐エミッタ電流がゼロにならないために生じる。

ロジック出力をバッファするためにバイポーラトランジスタを使用する際には、以上に述べたすべての考慮が必要になる。

・MOS FET

インターフェース回路としてMOS FETを使用する場合には、バイポーラトランジスタの場合とは異なる計算が必要となる。MOS FETはオンするために定常的な電流を必要としない。ゲートに電圧を印加することによってソース‐ドレイン間が低インピーダンスとなる。MOS FETの大きな利点は、低損失で電流を流せることである。例えば、米Supertex社の製品などは非常に高い電圧に対応することができる。昔のMOS FETは、オンするためのゲート‐ソース間閾(しきい)値電圧として10Vが必要であったが、製造プロセスの改良によって閾値電圧は大きく低下している。しかし、多くのMOS FETは、5VのロジックIC向けに設計されていたことに注意しなければならない。3.3V以下の電圧でもMOS FETがオンになるか否かは、データシートで確認する必要がある。

駆動電圧のほかにも問題がある。デジタルロジックICにとって、駆動される側のMOS FETのゲートはコンデンサとして働く。MOS FETが大きいほどその容量も大きくなる。CMOSロジックICもバイポーラロジックICもある程度の電流しか駆動できないため、MOS FETのゲート容量が大きいと、その起動は遅くなる。ここでも、ロジックICのデータシートによってワーストケースの仕様を確認しておく必要がある。電源電圧が最小の状態でロジックを動作させた場合に、MOS FETのオン、オフ動作の速度が設計目標に対し十分であるかどうかを確認しなければならない。

以上のような問題から、米Microchip Technology社の「TC4468」や米Texas Instruments社の「SN75372」など、MOS FETをドライブするためのICが開発された。ゲート容量の大きいMOS FETの駆動にはオペアンプを使用することもできるが、これには注意が必要である。MOS FETがオペアンプに与える容量性の負荷により、オペアンプの出力が変動する恐れがあるからだ。

さらには、ミラー(Miller)容量についても考慮しなければならない。ミラー容量とは、MOS FETにおけるゲート‐ドレイン間、またはバイポーラトランジスタにおけるベース‐コレクタ間の小さな浮遊容量のことである。ゲート電圧を上げるとドレイン電圧は下がるが、この低下はゲート電圧を上げようとする信号と相反することになる*1)。このため、トランジスタが現実世界の動作条件下で、期待通りに動作することを確認する必要が生じる。複数のデバイスを制御しなければならない場合は、単体のトランジスタではなく複数個のトランジスタを集積した高集積トランジスタアレイを使用するとよい。米Allegro MicroSystems社などからは、トランジスタアレイを集積したシングルチップの製品が提供されている。

脚注

※1…Israelsohn, Joshua, "Miller on edge: The role of Miller capacitance in nonlinear circuits," EDN, March 29, 2007, p.38. http://www.edn.com/article/CA6426883

Copyright © ITmedia, Inc. All Rights Reserved.