2007年10月31日、東京コンファレンスセンター・品川において、本誌主催『パワーマネジメントセミナー』が開催された。同セミナーの第3回目となる今回は、DC-DCコンバータの新たな進化の方向性を探ることをテーマとし、各講師に企業や大学で行われている最新の取り組み内容について語ってもらった。

3つの方向性

基調講演に登壇したのは九州大学 大学院 システム情報科学研究院 副研究院長の二宮保教授。『スイッチング電源の最新技術動向』と題した講演で、同氏はスイッチング方式のDC-DCコンバータ(以下、スイッチングレギュレータ)の過去から近未来までの進化の流れと、そこで用いられている中核技術について解説した。

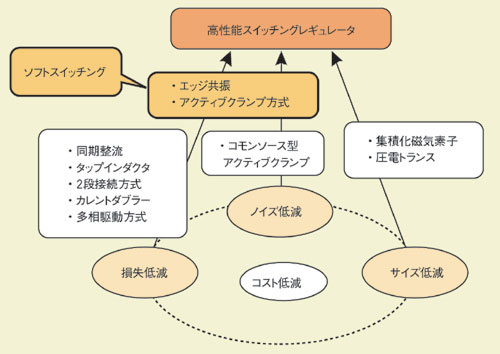

二宮氏は、スイッチングレギュレータの高性能化に向けた各種技術を、以下の3つに分類した。

・損失の低減

・ノイズの低減

・サイズの低減

その上で、各目的に応じた要素技術を図1のようにまとめ、それぞれについてこれまでの進化の歴史を振り返りながら解説を加えた。講演内容は多岐にわたったが、その中でも同氏が特に強調したのはソフトスイッチング技術である。

ソフトスイッチングは、スイッチング素子の共振現象を利用し、スイッチング素子への印加電圧が0Vあるいは導通電流が0Aになったところでスイッチのオン/オフ制御を行うというもので、損失の低減(効率の改善)に有効な技術である。これまで、スナバー回路やエッジ共振回路、サージエネルギのリカバリ回路、アクティブクランプ回路などを利用して実現されてきた。損失の原因となるスパイクやリンギングは同時にノイズの発生原因でもあるため、この技術はノイズ対策という面でも大きな効果をもたらす。同氏は、そのほかのノイズ低減手法として、コモンソース型アクティブクランプ方式やランダムスイッチング方式なども例に挙げた。ノイズの問題は、スイッチングレギュレータが抱える仕組み的な欠点ではあるが、こうした技術によりノイズの問題が解消されれば、これまでリニアレギュレータが利用されていた分野への適用がさらに広まると考えられる。

二宮氏の講演に続いて、各スピーカからそれぞれが携わる最新技術についての説明が行われた。以下、各講演のポイントを順に紹介する。

高周波化の実現手法

スイッチングレギュレータの制御方式に関する改善手法を紹介したのは、ナショナル セミコンダクター ジャパンのアナログ・ビジネス本部 パワープロダクト担当 アプリケーション・エンジニアリング・マネージャを務める若田部義明氏。同社製品に適用しているエミュレーテッド電流モード(Emulated Current Mode:ECM)方式を紹介した。

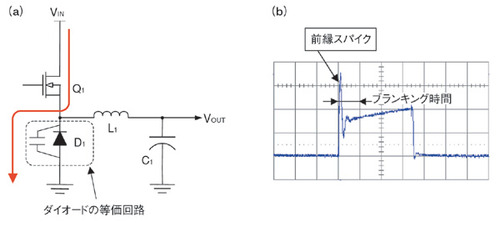

ECMが解決する課題は、通常の電流モードにおいて、高周波化の実現においてネックとなるブランキング時間の存在である。図2(a)において、MOS FETであるQ1がオンし、ダイオードD1がオフしたとき、D1には逆リカバリ電流が流れる。この電流によりPWM(pulse width modulation)回路部のコンパレータが誤動作するのを避けるために、通常、スイッチングレギュレータでは、前縁スパイクが発生している間をブランキング期間とすることで、制御回路がこのスパイク状の信号を検出しないようにする(図2(b))。このブランキング期間の存在が最小オン時間の制限事項となり、高周波化を妨げる要因となる。

それに対し、ECM制御方式では、ブランキング期間の電流波形を、スパイク成分を除いた形で別途等価的に求め、それを用いることで高周波化を実現する。具体的には、ダイオードD1に流れる電流をスイッチングが発生する直前にサンプリングし、その値とインダクタL1の出力端の電圧を基にして得たランプ電流値を加算する。その値を基に電流モード制御を行う。これにより、例えば入力電圧が高い場合でも、ブランキング期間による最小オン時間の制限を受けることなく、高周波化を実現することができるという。

スイッチングレギュレータでLDOの特性を改善

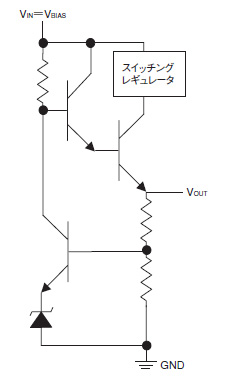

リニアレギュレータには、スイッチングレギュレータと比べて、設計が容易、ノイズが少ない、PSRR(power supply rejection ration)特性に優れる、高速応答特性を備えるといった利点がある。しかし、効率の面ではスイッチングレギュレータに見劣りする。マイクレル・セミコンダクタ・ジャパンでシニアFAEを務める大貫徹氏は『LDOレギュレータのさらなる高性能化』と題した講演で、LDO(low dropout)レギュレータの回路構造の一部にスイッチングレギュレータを適用することで、リニアレギュレータとしての特性を生かしつつ、損失を改善する手法である「SuperLNR」を紹介した。

この手法のベースとしているLDOレギュレータは、構造的に優れたPSRR特性が得られるnpn型のリニアレギュレータである。この方式の場合、変換元となる入力電圧とは別に、それより高いバイアス電圧も必要となる。しかし、実際の機器の基板上には都合の良い入力電圧、バイアス電圧の組み合わせが存在するとは限らない。そこで、図3のようにnpn型のリニアレギュレータとスイッチングレギュレータを組み合わせた構成とし、基板上で広く使われている5V、3.3Vといった電圧を受け取る。この電圧をバイアス電圧として使用し、さらにそれをスイッチングレギュレータによって降圧し、それを変換元となる入力電圧として利用しようという考え方である。

この方式を使用した同社製品では、入力電圧範囲が3.0V〜5.5V、出力電圧の下限が1.0Vで、出力ノイズが最大5mV、PSRRが1kHzのポイントで70dB、10kHzのポイントで60dBという値を実現しているという。

コイル/トランスを排除してオンチップ化

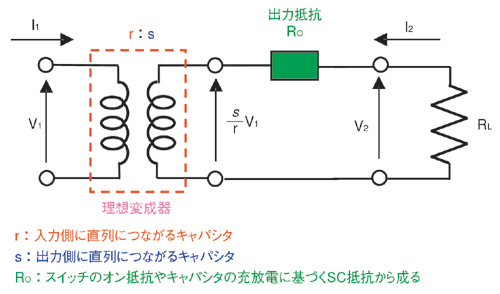

コイル/トランスを使用しないでスイッチング電源を実現し、それをシステムLSIに統合するオンチップのDC-DCコンバータとして利用しようという考え方がある。その実現手段の1つがスイッチトキャパシタ(SC)電源である。熊本電波工業高等専門学校 情報通信工学科の大田一郎教授は、SC電源の理論や試作品の評価結果などを交えてその可能性について説明した。

SC電源では、複数のキャパシタ(MOS容量)とMOSスイッチで構成されたSC変成器を利用する(図4)。例えば、2個のキャパシタを並列に接続して入力電圧まで充電し、それを直列につなぎ直して出力に接続すると、入力電圧の2倍の電圧が得られる。キャパシタ間の接続をスイッチで任意に切り換えることで、昇圧、降圧、極性反転を行う仕組みだ。

大田氏らが試作したSC電源では、最大出力電流が512mA、最大出力電力が1.15Wで、88.5%の効率が実現できたという。ただし、現状ではチップサイズが大きいことや外付け部品が数個必要となるなど、「価格の面で、即商用化するのは難しい」(大田氏)という状況だ。しかし、磁性雑音に対する要求が厳しい用途や、電源の薄型化が求められる用途、速い負荷応答が求められる用途、入出力電力比があまり変化しない用途などでは将来性が期待できる技術だという。

Copyright © ITmedia, Inc. All Rights Reserved.