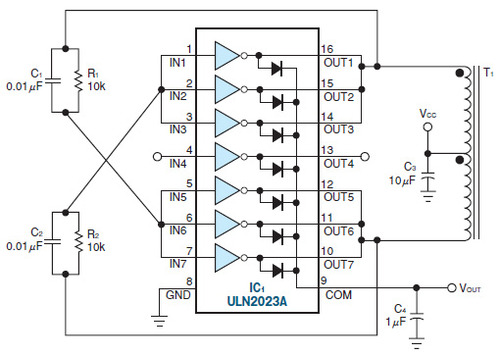

広い範囲の入力電圧に対して使用可能で、少数の部品で構成できる倍電圧電源を紹介する。その電源回路は、1個のトランスを使用するプッシュプル型DC-DCコンバータの動作が倍電圧動作になることを利用して構成する。スイッチング素子には、高電圧動作が可能なダーリントン接続トランジスタで構成したドライバアレイ「ULN2023A」(米Allegro MicroSystems社製)を使用する。これは5Vから30Vという広い入力電圧範囲で動作し、標準的には1Wから4Wの範囲の電力を比較的高い効率で出力できる。

図1に示したのは1個のトランスを用いたプッシュプル型DC-DCコンバータの基本構成である。図のように、トランジスタQ1とQ2のコレクタはRC回路網経由で他方のトランジスタのベースに接続されている。これによりフィードバックループが形成され、発振が持続する。この回路の定常動作では、トランスが正負の方向の飽和レベルまで交互に励磁される。それに対応して、トランスのセンタータップ両側の巻き線に交互に電圧が誘起される。これに伴って各トランジスタが交互にオン/オフする。その動作周波数は、入力電圧とトランスコアの飽和特性から次式によって計算できる。

ここで、VCCは入力電圧、βSは飽和磁束密度(単位はガウス)、Aはコアの断面積(単位は?2)、Nはトランス巻線数の1/2である。

この回路では、各トランジスタのコレクタ‐エミッタ間電圧は入力電圧VCCの約2倍とインダクタンスによって誘起される電圧とを加算した値になる。Q1とQ2のコレクタ電圧をダイオードD1とD2により整流して平滑化したものが出力電圧となる。この電圧は入力電圧VCCの約2倍に相当する。

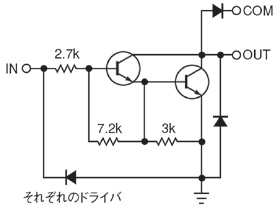

図2に示したのは、ULN2023Aの内部構成である。このように、トランジスタのコレクタ出力には整流用ダイオードが接続されている。図1の回路は、これを利用して構成する。

ULN2023Aの降伏電圧は95Vである。この値は、入力電圧VCCを30Vとしたとき、その2倍の電圧と、過渡的に発生する励起電圧を加算した値よりも大きい。また、同製品が備えるトランジスタのコレクタ‐エミッタ間飽和電圧は100mA程度のコレクタ電流に対しては十分に小さい。また、スイッチング時間も短く、数十キロヘルツオーダーのスイッチング周波数を得ることができる。

図3に、同製品を利用した倍電源電圧回路を示した。3チャンネル分のドライバを並列接続したものによってトランスを駆動するため、コレクタ‐エミッタ間電圧が小さく抑えられ、許容電力を大きくとることができる。

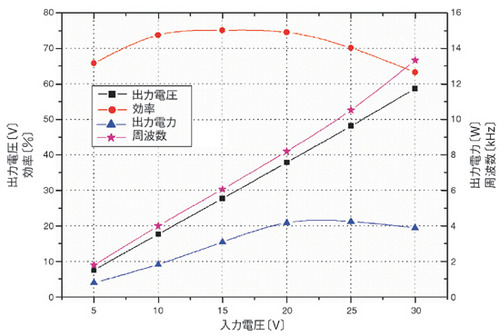

表1に示したのは、5V〜30Vの入力電圧に対して倍電圧動作を行った際の各種パラメータの計測結果である。また、この結果をグラフ化したものを図4に示す。この入力電圧範囲における入力電流は300mA以下となる。ここで紹介した倍電圧回路が、低電力の用途に適し、広い入力電圧範囲に対して比較的効率良く動作することが見てとれる。

Copyright © ITmedia, Inc. All Rights Reserved.