FPGA⇒ASICを成功に導く8つのポイント(2/3 ページ)

FPGAは、特にプロトタイプ開発や少量生産などで大きな威力を発揮するデバイスである。しかし、FPGAで実現した機能をASICに移行することで、より多くの利点が得られるケースも少なくない。その移行をシームレスに行うために、基板設計とチップ設計の両面から見てポイントとなる事柄を説明する。

ポイント4 IPの採用は慎重に

ASICへの移行を容易にするために、FPGAを設計する際にできることがいくつかある。最初に考えるべきことは、IP(intellectual property)の選択である。IPには、積和ユニット、メモリー、FIFO(first in first out)ジェネレータなどのシンプルなブロックもあれば、プロセッサ、高速シリアルI/O、SERDES(serializer/deserializer)などのより複雑なブロックもある。通常、これらのブロックにはIPライセンスの問題があり、その多くはFPGAベンダーの専有技術となっている。

一見、FPGAの豊富な無償IPのリストは魅力的なものだ。しかし、実際には大量に生産されるシステムを対象としている場合、FPGA自体が高価であるために、無償IPのメリットが意味をなさない可能性がある。ASICへの移行を行うのであれば、さらに問題は複雑になる。

このような理由から、FPGAベンダー専有のIPに縛られないようにする戦略が必要である。設計を開始する前に、ASICへの移行時のIPの取り扱いに関する方針を作っておくとよい。例えば、FPGA内でネイティブなブロックに存在するメモリーを使用するのはよいが、より高度なFIFOジェネレータを使用すると、それがFPGAベンダーの専有IPである可能性がある。論理合成ツールのベンダーが提供するFIFOモジュールを使用するか、ASICベンダー経由でFPGAのIPを使用する許可を得るほうがずっと容易かもしれない。

一般的には、できれば論理合成が可能なIPを利用すべきである。設計前にIPのライセンスを取得し、FPGAとASICの両方で利用できるようにしておくとよい。ASICベンダーとともに、IPに関する方針を策定しておくとよいだろう。また、ASICベンダーは、認定IPベンダーやASICデザインハウスが保有するIPについて何らかの提案をしてくれるかもしれない。FPGAベンダーが提供するIPを利用すると決定してしまい、ASIC用には追加のライセンス料を支払わなくてはならない状況に陥る前に、ライセンスに関する交渉を行うことが重要である。

ポイント5 タイミング制約を把握する

タイミング制約などの基本的な仕様も考慮すべきポイントである。例えば、FPGAにおけるNANDゲートはどのくらいの速度で動作し、ASICのNANDゲートはどのくらいの速度で動作するのだろうか。重要なのは、システムで必要となるのは、どれくらいの速度で動作するNANDゲートなのかということだ。システム内で動作するチップのタイミング仕様は重要であり、システム全体のタイミング制約を理解するのはさらに重要なことである。

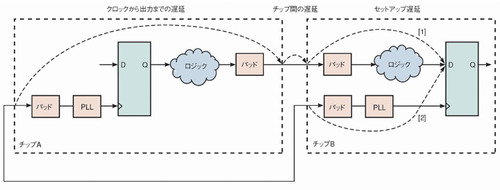

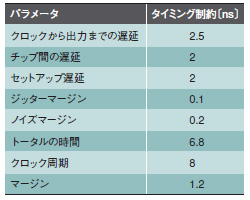

図1はタイミング制約を満たしながら動作する2つのチップの概要を表している。タイミングに関する各種パラメータの具体的な値は表1のようなものとなる。

マージンも含めて、タイミング制約に関するすべてのパラメータを理解しておくことは、移行作業に役立つ。ASICにおいてより低コスト化が図れる技術を利用できるのならば、移行を担当する技術者は、全体的な制約を満たしつつ、さまざまなタイミングパラメータを調整することになるだろう。逆にタイミング制約を理解していなければ、FPGAのタイミングパラメータの範囲を超えてしまい、不要なコストがかかる可能性がある。設計に用いた技法や、特別なタイミング要件、起動時の要件、電源停止モードなど、設計に関する特記事項はすべて列挙しておくことが重要である。移行後のチップが意図どおりに動作することを保証するためには、これらの情報が必要となる。

移行作業は、おそらくRTLコードから開始することになるだろう。その際には、コードが整理されていてドキュメント化されていると都合が良い。FPGAの設計者は、合成用スクリプトとタイミング制約ファイルを提供する必要がある。回路の一部または全体をネットリスト形式で提供しなければならないケースもある。その場合にも、構成を示すドキュメントや、合成用スクリプト、タイミング制約ファイルが存在することが望ましい。回路によっては、移行の成否を検証したり、電力シミュレーションを実行したりするためのテストベンチを提供すべきだろう。

有用なテストベンチを作成するためには、入力のキャプチャと応答の予測が行えるか否かがカギとなる。この情報を提供する最良の方法は、端子の状態変化を記述するVCD(value change dump)ファイルを使用することである。正確なタイミングでの情報が必要となるので、キャプチャシミュレーションは許容遅延モード(assignable delay mode)、またはフルタイミング精度で実行することが必須だ。ゼロ遅延モードやユニット遅延モードでは、端子のデータファイルに正確な値を反映させることができない。

ポイント6 起動設定についての考察

起動時に長大なプログラミングと構成シーケンスが必要なFPGAとは異なり、ASICは本質的にそのまま使用可能な部品である。しかし、ASICへの移行を前提にするなら、FPGAの設計を開始する時点で、起動時の振る舞いについても注意を払っておく必要がある。FPGAのプログラミングによって実現される機能や信号にシステムが依存する場合、ASICに移行した際に問題が生じないようにしておかなければならない。依存の可能性がある例としては、プログラミングが正しく行われたことを確認するため、あるいはシステムリセットの解除や別の起動シーケンスの一部で、「done」端子を監視している場合などが挙げられる。ほかの例としては、いくつかのFPGAのうちのいずれかをASICに移行することなくそのまま使用することを計画しており、なおかつ複数のFPGAをデイジーチェーンとして扱って構成を実施するようなケースにも注意が必要である。

もう1つ、起動に関して考慮しなければならないのは、アナログ的に行われるPOR(power on reset)を適切に処理することである。異なる製造工程で製造されたFPGAのPORが、まったく同じように動作することを期待してはならない。当然、ASICのPORとFPGAのPORも完全に同じ動作とはならない。システム全体用のPOR信号を生成するチップがシステム内に1つだけ存在するようにするのが良い設計である。これにより、タイムシーケンスの問題が生じる可能性が抑えられ、システムの起動の信頼性を高めることができる。POR信号の生成には、FPGA/ASICのどちらを使用してもよいが、その機能を担うチップはシステム内にただ1つにすべきだということである。

Copyright © ITmedia, Inc. All Rights Reserved.