マルチストローブによるソース同期I/Fの試験:タイミングマージンの減少に対処(2/2 ページ)

データ転送を高速に行う最近のICは、外部インターフェースとして、ソースシンクロナス方式を採用している。このインターフェースをICの自動試験装置(ATE)によって正確に試験するには、タイミングマージンの減少に対処しなければならない。本稿では、その対処法としてマルチストローブを用いる手法を紹介する。

出力依存タイミング法

低いクロック周波数で動作するソースシンクロナスI/Fにおいて、リファレンスクロックと出力クロックの間のスキューが静的で変動しないのであれば、上述した問題への対処は容易である。その場合、「出力依存タイミング法(output dependent timing)」と呼ばれる手法を用いればセットアップ時間、ホールド時間の試験を行うことができる。この手法では、まず、ストローブ信号をスイープしながら計測を行っていく。その結果から実際に試験する際に用いるストローブ信号の正確なタイミング(リファレンスクロックとの位相差)を求めて、以後のIC試験に適用する。この試験手法が適用できるのは、上述したようにデータ信号とリファレンスクロック間の位相差が安定している場合に限られ、大きなドリフトやジッターが含まれている場合には適用できない。

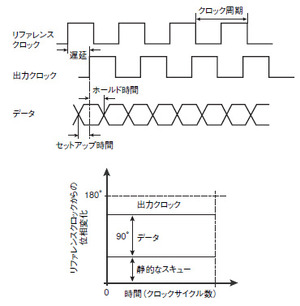

図1は静的なスキューのみが生じる場合のタイミング関係を表している。試験時には、リファレンスクロックはATEシステムから対象とするICに供給されるが、静的なスキューのみが生じる場合、リファレンスクロックと内部回路で生成された出力クロックの位相関係は一定で変化しない。従って、出力クロック/データに対して一定の位相差を有する固定ストローブ(固定位相ストローブ)を使用することにより、セットアップ/ホールド時間の試験が行える。

出力依存タイミング法の限界

特性試験が困難になるのは、ジッターなどによる位相の変動が相対的に無視できないほどI/Fのクロック周波数が高い場合である。

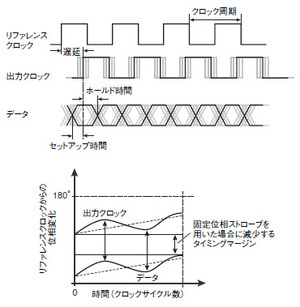

データと出力クロックが同期していることと、両者がほぼ同じ経路を伝送されることから、両者にほぼ同等の位相ジッター/ドリフト(以下、共通位相ジッター/ドリフト)が生じる。このような位相の変動は、実際のIC間におけるデータの送受信には影響がない。しかし、固定位相ストローブを利用した出力依存タイミング法によって信号の試験を行おうとした場合、共通位相ジッター/ドリフトが大きくなると、位相が時間の経過に伴って変動することでタイミングマージンが減少し、出力クロック/データの位相遷移が固定位相ストローブに相応しなくなる(図2)。

つまり、共通位相ドリフト/ジッターの影響で固定位相ストローブを基準にして観測したアイパターンが出力クロックを基準にして観測したものと比較して閉じる。そのため、ICの実使用時よりも試験時のほうが厳しい条件になってしまうのだ。まとめると、動的に位相が変化する場合、出力依存タイミング法ではソースシンクロナスI/Fのセットアップ時間/ホールド時間などのタイミングデータを正確に試験できなくなるということである。

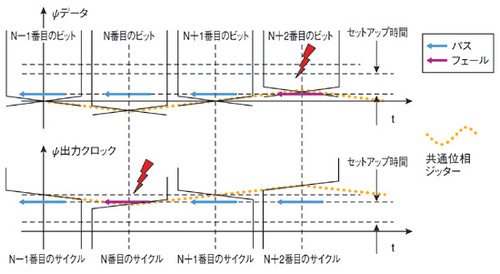

図3に共通位相ジッターの影響を示す。これは、データと出力クロックのリファレンスクロックに対する位相が、サイクルごとに反時計方向に90゚単位で回転した場合を表している。この図から、データと出力クロックの遷移点が時間(サイクル数の増加)に伴って変化する様子が理解できるだろう。テストのために印加しているジッターは、正弦波に沿って変化している。ジッターが最小の場合、データと出力クロックの遷移点は左向きの矢印で示した固定位相ストローブによるラッチタイミングに対して余裕がある。しかし、赤い稲妻マークで示した部分では、ジッターの影響で固定位相ストローブによるラッチタイミングに余裕がなくなっていることがわかる。

マルチストローブ手法

上述したように、固定位相ストローブによる試験手法には限界がある。これへの対処として、筆者らはソフトウエアベースの検査手法を開発した。その手法を用いれば、ドリフトやジッターなどにより対象となる信号の位相が動的に変動する場合でも、問題なく試験が行える。

また、この手法は、従来から活用されている「捕捉比較ピンエレクトロニクス(capture and compare pin electronics)」とソフトウエアをベースとしている。そのため、使用する各社試験装置のハードウエアに適合可能な柔軟性がある。

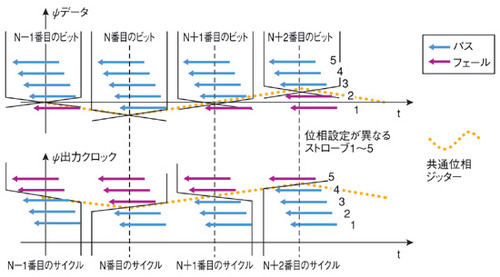

筆者らの手法と従来の手法との大きな違いは、筆者らの手法ではマルチストローブを使用することだ。つまり、出力クロックとデータにおけるセットアップ/ホールド時間の位相の変化に応じて、試験が可能な位相のストローブを複数のストローブから選択して用いる。複数のストローブのうち少なくとも1つが、対象とするICの出力クロック/データにおけるセットアップ時間とホールド時間の規格値を満たすかどうかを試験できればよいのである。エラーの発生しない(フェール判定とならない)ストローブの位相は固定ではなく、図4に示すように出力クロック/データの各ビット(サイクル)ごとに変化する。1つのサイクルにおいて、少なくとも1つのストローブの位相設定が適切であれば、そのサイクルにおけるセットアップ時間やホールド時間の試験が行える。

図4を用いてもう少し具体的に説明すると、N−1番目のサイクルでは、データに対してストローブの位相設定の2〜5が有効であり、出力クロックに対してはストローブの位相設定の1〜3が有効である。ストローブの位相設定の2と3は、データと出力クロックの両方に対して有効であり、この位相設定によるストローブを用いれば試験が成立する。このような試験手法を効果的に使用するには、試験パターンが繰り返されることと、マルチストローブにおけるストローブ間の位相差(ステップ)が十分に小さいことが必須である。

この手法ならば、ジッターによってサイクルごとに位相が変化しても正確な検証が行える。例えば、1つのサイクルに少なくとも1つの有効なストローブが存在し、その1つのストローブを用いて行った試験の結果がフェールにならなければ、そのサイクルは仕様を満たしたことになる。あとは、これを全試験パターンにおいて実施すればICの特性試験が行えることになる。

この手法を用いれば、共通位相ジッター/ドリフトの振幅/波形/周波数成分などの解析も行えるので、不良品の解析にも適用可能である。

製造ラインでの試験

製造ラインにおける試験では合否判定さえ行えればよい。つまり、特性試験とは違い必ずしも測定値を必要としない。その代わり、合否判定の結果は高速に得られなければならない。マルチストローブを用いたセットアップ/ホールド時間の試験では、複数のテストパターンを生成する時間やそれをロードする時間、エラーデータを解析する時間を要する。そのため、テストパターンが長くなり、位相を走査する範囲が広がると製造ラインで用いるには試験時間が長くなり過ぎてしまう。

試験時間を許容できる範囲に収めるためには、2つの重要な要因に注目すべきである。1つは、テストパターンを走らせた際に発生する大量のエラー情報を取得できる性能を確保すること。もう1つは、試験装置に取り込んで処理するデータの量を最少にすることである。

筆者が所属するVerigy社の半導体試験装置「V93000」の場合、ピンエレクトロニクス部にマルチストローブによる試験アルゴリズムが実装されている。それによって、サイクルごとの測定結果をブール代数に変換し、試験装置に取り込むことができる。このことが、ピンエレクトロニクス部とコントローラ部の間で通信するデータ量を抑えることにつながる。また、追加のオプションを使用すれば、試験装置内のハードウエアによって合否判定を行うことができる。それを用いれば、試験速度を数桁も向上できる。

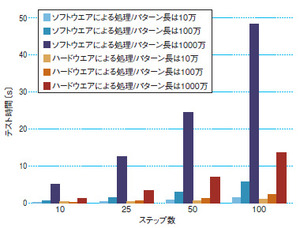

ストローブの位相のステップ数やテストパターン長、ハードウエア/ソフトウエアによる処理方法を変更した場合のソースシンクロナスI/Fに対する試験時間の違いを図5に示す。量産品の試験時間はその製品のコストに反映されるが、例えば、テストパターン長が1000万で位相のステップ数が100の試験を行う場合でも、合否判定を試験装置のハードウエアで行えば、その試験時間は許容範囲に収まるだろう。試験装置が採用している処理方法にもよるが、実運用時には、試験カバレッジとステップ数/テストパターン長のトレードオフを見極めて適切な選択を行わなければならない。

Copyright © ITmedia, Inc. All Rights Reserved.