DC-DCコンバータのノイズ対策[実践編]:徹底研究! 設計/実装における具体策(1/5 ページ)

本稿では、非絶縁型/スイッチング方式のDC-DCコンバータにおけるノイズ対策について、2回にわたって解説している。前回は『理論編』として、ノイズの種類やその発生メカニズムについて説明した。その内容を踏まえ、今回の『実践編』では、ノイズの発生を抑えるための基板レイアウト設計の基本、部品の選択方法、付加回路による対策手法について具体的に解説する。

3つの観点

前回の『理論編』で解説したとおり、非絶縁型/スイッチング方式のDC-DCコンバータでは、主に寄生インダクタの影響により、ハイサイド/ローサイドのパワーMOSFETのターンオフ時に発生する高周波のスパイク/リンギングがノイズとして問題になる。今回は、この問題に対して、機器のプリント配線板(以下、基板)の設計はどのように行えばよいのかを具体的に説明する。本稿を読み進めるに当たっては、本誌12月号の『理論編』またはそのウェブ版を参照して用語の定義などを確認しておいていただきたい。

さて、非絶縁型DC-DCコンバータのノイズ対策、特に数百MHzの周波数帯のノイズに対しては、以下の3つの観点から対策を考えることになる。

(1)基板のレイアウト

(2)部品の選択

(3)付加回路による対策

まず、設計段階で基板のレイアウトと部品の選定の面で十分にノイズ対策の方法を練っておく。そして、最後は実機で評価を行い、付加回路による対策を施すというアプローチになる。

以下、上記の3項目について順に説明していく。

基板のレイアウト

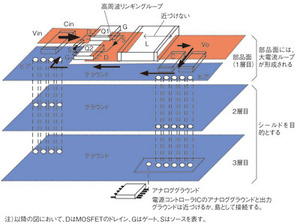

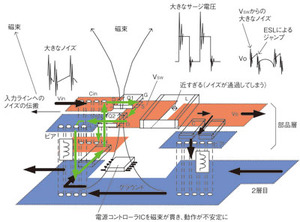

図1に示したのは、現実的で、しかも問題の少ない基板レイアウトの例である。この図を基に、ポイントとなる部分の詳細を以下に述べる。なお、図2にあまり好ましくない例も示しておくので、随時参照されたい。

■パワーステージ全体

入力コンデンサCin、ハイサイド/ローサイドのパワーMOSFETであるQ1、Q2、出力インダクタL、出力コンデンサCで構成されるパワーステージには、大きなパルス電流が流れる。図1に示すように、この部分のレイアウトは、グラウンドパターンも含めて部品面(1層目)に形成する。また、非絶縁型DC-DCコンバータの場合、パワーステージの入力側のグラウンドと出力側のグラウンドは、2つに分けずに1つの“島(アイランド)”として形成する。

大電流が流れるこのパワーステージのループには、図2に示した好ましくない例のような形でビアを使うのは避けるべきだ。ビア自体が数nHの寄生インダクタンスを持つからである。また、仮に数多くのビアを設けても、数百MHzといった高周波信号はおそらく一部のビアしか通過しないので、多数のビアによるインピーダンスの低減効果はあまり期待しないほうがよい。

■内層のベタグランド

図1の2層目、3層目に示すように、内層はベタグラウンドとし、部品面のグラウンドからできるだけ多くのビアでベタグラウンドに低インピーダンスで接続するとよい。内層のベタグラウンドによってシールド効果が向上するので、仮にCin、Q1、Q2から成る高周波リンギングループや出力インダクタ、出力コンデンサの真下に電源コントローラICが配置されていたとしても、動作が不安定になってしまうリスクはある程度低減される。

なお、内層のベタグランドはあくまでもシールド用であり、ここに大電流を流す意図はない。

■高周波リンギングループ

特に重要なのは、高周波リンギングループにおける寄生インダクタンスを1nHのレベルで考慮して小さくすることである。ストリップラインの場合、簡単に言えば1mmが約1nHに相当する(正確には、幅と長さで決まる)。従って、1mmの長さを惜しんで高周波リンギングループのレイアウトを小さくすることが重要だ。

また、仮にレイアウトが理想的であっても、パワーMOSFETのパッケージによる問題が発生することがある。例えば、SOP-8パッケージでは、リードと内部のボンディングワイヤーだけで数mmの距離がある。そのため、ここですでに数nHのインダクタンスが存在し、1/2LI2で表されるノイズのエネルギーが生じてしまう。

後ほど、付加回路による対策のところで述べるが、ハイサイドMOSFETのゲート抵抗(ゲート入力部に直列に付加する抵抗)とローサイドMOSFETの両端のスナバー(snubber)回路を追加することでノイズ対策が行える。基板には、あらかじめそのための部品の座を設けておくとよい。

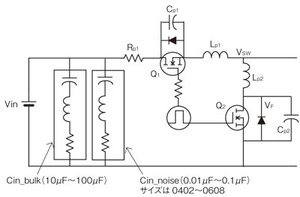

■入力コンデンサ部

高周波リンギングループで問題になるのは、パワーMOSFETとレイアウトの寄生インダクタンスだけではない。入力コンデンサのESL(等価直列インダクタンス)も大きく影響する。よって、図3に示すように、入力コンデンサの部分は、入力コンデンサ本来の役割を果たすもの(バルクコンデンサ)として10μFもしくはそれ以上のセラミックコンデンサと、ノイズ対策用(デカップリング用)として0.1μF程度のセラミックコンデンサを組み合わせるとよい。0.1μF程度で1608サイズ、0603サイズといったセラミックコンデンサはパッケージサイズが小さいので、ESLも小さいし、Q1、Q2の直近に配置できる。

なお、バルクコンデンサのサイズが大きくて、どうしてもQ1、Q2の近く(数mm以内)に配置できない場合には、ノイズ対策用の0.1μF程度のセラミックコンデンサを、ビアを介さずにQ1、Q2と同一面に配置し、バルクコンデンサはビアを通して裏面に配置するとよい。後で示す実験結果からもわかるのだが、入力端子部におけるノイズ電圧のうちリップル分はごくわずかであり、ほとんどがコンデンサのESLによるスパイク/リンギング電圧である。従って、容量の大きさよりもESLの小ささを優先し、0.1μF程度のセラミックコンデンサを入力端子部の直近に設置しておけば、ビアを介してバルクコンデンサを裏面に設置しても、ノイズのリスクをかなり低減できる。もちろん、バルクコンデンサもQ1、Q2と同一面でなるべく近くに配置するほうがよいことは言うまでもない。

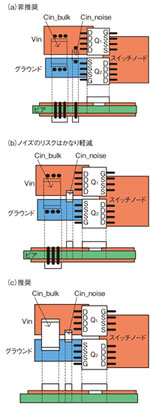

図4は、入力コンデンサ部の代表的なレイアウト例である。図4(a)では、バルクコンデンサCin_bulkと0.1μF程度のノイズ対策用セラミックコンデンサCin_noiseの両方とも、ビアを介して裏面に配置している。この部分のESLがLdi/dtで決まるノイズを引き起こすので、このレイアウトは推奨できない。一方、図4(b)ではノイズ対策用のセラミックコンデンサCin_noiseは部品面にあり、Q1、Q2の直近に配置されている。そのため、高周波のスパイク/リンギングはかなり低減されることが期待できる。実装面積に制約がある場合、この方法は現実的な解だと言える。

理想的なレイアウトは図4(c)である。このレイアウトでは、バルクコンデンサCin_bulkもノイズ対策用コンデンサCin_noiseも部品面に配置している。しかも、Q1、Q2の直近に配置しているので、最も良いレイアウトだと言える。

Copyright © ITmedia, Inc. All Rights Reserved.