A-Dコンバータが支えるCMOSイメージセンサーの進化(1/2 ページ)

CMOSイメージセンサーは、高精細なビデオ画像を素早く取り込めるものでなければならない。その上で要となるのが、同センサーが内蔵するA-Dコンバータだ。本稿では、CMOSイメージセンサーが内蔵するA-Dコンバータのアーキテクチャの変遷を中心に、これまでの技術的な進化の流れについて解説する。

2つのアーキテクチャ

CMOSイメージセンサーは、この2年間で大きく進化した。これに大きく寄与したのが、同センサーが内蔵するA-Dコンバータに対して行われた改良であることは間違いない。

CMOSイメージセンサーには、大別すると、2種類のA-D変換アーキテクチャが採用されてきた。パイプライン型とカラム(列または列並列)型である。CMOSイメージセンサーの大手ベンダーは、これらのどちらか、あるいは両方のA-D変換アーキテクチャを製品に適用してきた。

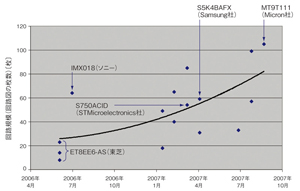

筆者は、各社のCMOSイメージセンサーについて調査を行い、2種類のA-D変換アーキテクチャの長所と短所を比較した。調査の対象としたのは、韓国Samsung Electronics社、米Micron Technology社*1)、ソニー、東芝 セミコンダクター社、スイスSTMicroelectronics社の各製品である。本稿では、その内容を紹介することで、A-Dコンバータの進化が、CMOSイメージセンサーをどのようにして支えてきたのか説明する。

イメージセンサーの基本構成

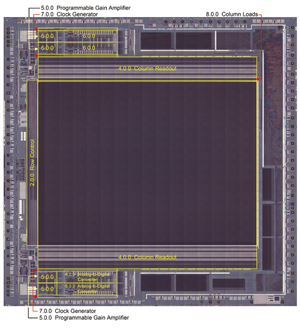

筆者は、各社CMOSイメージセンサーのチップ(ダイ)を観察し、ソフトウエアを活用して回路を抽出した。それによって得られた各製品の回路図を基に、CMOSイメージセンサーを構成する各回路について整理した。その結果、さまざまなことがわかってきた。例えば、CMOSイメージセンサーの解像度が高まるとともに、多くの機能がチップに集積されるようになった。このことは、筆者の行った作業においては、アナログ信号パスを書き表した回路図の枚数が大幅に増えてきたことから見てとれた(図1)。

最新のCMOSイメージセンサーは、1個のチップ上に、フォトダイオードの画素(ピクセル)マトリクスアレイ(画素行列アレイ)、A-Dコンバータ、デジタル画像処理回路などを集積している。これらは、必ずしもノイズの少なくない環境で光を取り込み、画像データを確実に出力するためのものである。

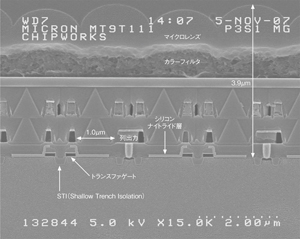

センサーに入射した光を電気信号に変えるフォトダイオード部は、光をフォトダイオードへと集めるマイクロレンズを内蔵している(写真1)。なお、フォトダイオードの一部は、読み出し回路の金属層によって入射光を遮へいするようになっている。最先端のイメージセンサーの画素寸法は1.4μm角ほどしかない。

ほかのIC製品と同様に、CMOSイメージセンサーでも、回路規模を抑えてチップ面積を節約することが基本的には望ましい。そのため、読み出し回路のトランジスタを複数の画素で共有するチップが少なくない。ウェーハ1枚からとれるチップ数をなるべく多くするためである。

なお、一眼レフタイプのデジタルカメラでは、35mmフィルム相当の大きさの画像を取り込まなければならない。イメージセンサーはそれなりの大きさになるので、製造歩留りの向上を重視した設計を行う必要がある。

最近のCMOSイメージセンサーでは、大型でスタンドアロンのパイプライン型A-Dコンバータはあまり用いられなくなってきた。その代わりに、画素アレイの各列にA-Dコンバータを搭載したシングルスロープのカラム型A-Dコンバータが用いられるようになってきている。このカラム型A-Dコンバータの利点は、センサーからのデータをより迅速に取り出せることだ。各A-Dコンバータがデータを処理する時間をかなり長くとれることになり、それぞれがセトリング時間を長く確保できることから、ノイズが少なく、高い精度のデータが得られる。

パイプライン型A-Dコンバータ

当初、CMOSイメージセンサーは、先に製品化されていたCCDイメージセンサーをひな形として開発された。そのため、初期のCMOSイメージセンサーのアーキテクチャは、CCDイメージセンサーのそれと同様のものであった。

次の世代のCMOSイメージセンサーでは、CMOSイメージセンサーのチップ自体にA-Dコンバータを内蔵するようになった。使われたのは、パイプライン型のA-Dコンバータである。パイプライン型A-Dコンバータは高速な変換が可能であり、フォトダイオードの画素行列アレイの全画素を処理するのに十分なものだった。ただし、遅延時間が長いので、そのことが問題にならない用途で使われていた。

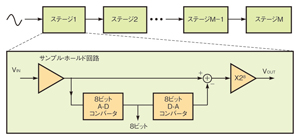

初期のパイプライン型A-Dコンバータは、単一の単純なパイプライン構成をとっていた(図2)。昨今のパイプライン型A-Dコンバータは、DDR(Double Data Rate)方式でフル差動のマルチパイプライン構成へと発展している。

フォトダイオードからA-Dコンバータまでのアナログ信号回路は、ベンダーが異なってもほぼ同様のものが用いられている。まず、画素行列アレイの行を選択し、列に対応する回路に信号を転送して、相関2重サンプリングによって信号を得る。

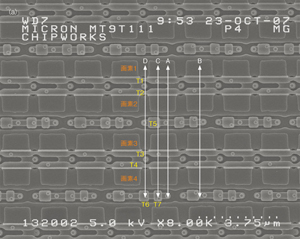

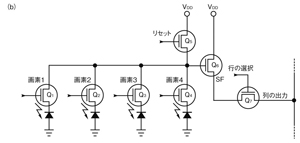

画素行列アレイ内のトランジスタ数を減らすために、多くのベンダーは読み出しトランジスタとリセットトランジスタを複数の画素で共有するアーキテクチャを採用している。例えばMicron社のCMOSイメージセンサー「MT9T111」(1/4インチ、300万画素)は4画素で3個のトランジスタを共有している。合計で7トランジスタであることから、1画素当たりの換算トランジスタ数は1.75となる(図3)。

図3 画素行列アレイのトランジスタ構成 (a)は、CMOSイメージセンサー「MT9T111」の観察像。A、B、C、Dの各線は、さらに詳しく解析するための切断面を意味する。(b)のように、1画素当たり、1.75トランジスタで構成される。

読み出し時には、まず、行の選択が行われる。続いて、選択された行と列の出力線が接続される。出力信号は、画素アレイ端にあるピッチ整合型の列並列サンプリング回路へと送られる。通常は、信号をマルチプレクサに送り、複数の列が同じアナログ処理列を利用できるようにする。この手法を使うことで、プレビューやダウンスケーリングなどの高速な画像読み出しが必要なときに、画素のサブセットだけを選択できるようになる。また、アクティブ負荷が、信号のバイアスとクランプのために配置してある。

それから信号は、相関2重サンプリング回路に送られる。同回路では、まず、黒レベル検知用に金属層によって光を遮へいしたフォトダイオードから信号(黒レベル信号)を読み出す。続いて、実際の画素の信号を読み出して黒レベル信号の分を差し引くことで、出力信号のレベルを決める。パイプライン型A-Dコンバータを内蔵したアーキテクチャでは、ピッチ整合型列回路からA-Dコンバータへの信号の多重化が行われる。

CMOSイメージセンサーが内蔵するA-Dコンバータは、1個であるとは限らない。要求仕様(動作速度および周波数帯域)に応じ、内蔵するA-Dコンバータの数は決められる。例えばMicron社のデジタルカメラ向けCMOSイメージセンサー「MT9E001」は、12ビットのA-Dコンバータを4個搭載している(写真2)。これによってCCDイメージセンサーを上回る動作速度を達成している。

Micron社のMT9T111とMT9E001は、いずれも、DDR方式/完全差動のパイプライン型A-Dコンバータを内蔵している。両製品は、400mWの消費電力で96メガビット/秒のデータレートを実現する。

DDR方式の特徴の1つは、デュアルパイプライン構成のA-Dコンバータが1つのオペアンプを共有することだ。これにより、クロックサイクルごとに2つのデジタルデータに相当するサンプリングと変換動作を実行できる。

チップのレイアウトは簡単ではない*2)ものの、コンデンサを整合させることで、12ビット精度は十分に実現可能である*3)。

脚注

※1…(編集部注)現在、Micron社のイメージセンサー事業は、子会社のAptina Imaging社が担当している。開発と販売はAptina社、製造はMicron社が担っている。

※2…Nagaraj, K, HS Fetterman, J Anidjar, SH Lewis, and RG Renninger, "A 250-mW, 8-b, 52-Msamples/s parallel-pipelined A/D converter with reduced number of amplifiers," IEEE Journal of Solid-State Circuits, Volume 32, Issue 3, March 1997, p.312

※3…Kwang-Bo Cho, Chiajen Lee, S Eikedal, A Baum, Jutao Jiang, Chen Xu, Xiaofeng Fan, and R Kauffman,"A 1/2.5 inch 8.1Mpixel CMOS Image Sensor for Digital Cameras," International Solid State Circuits Conference, IEEE International Digest, February 2007, p.508

Copyright © ITmedia, Inc. All Rights Reserved.