高速化が進むSPICEシミュレータ(3/3 ページ)

アナログ回路のシミュレーションにおいては、現在でもSPICEが主役を務めている。しかしながら、ICに集積される回路の規模が膨大なレベルになるに連れ、従来のSPICEシミュレータでは、現実的な時間内に結果を得ることが難しくなった。この問題に対して、SPICEツールベンダーは、どのように取り組んでいるのだろうか。

■Gemini社

米Gemini Design Automation社も、マルチスレッドによって性能向上を実現している。SPICE精度のツールと高速MOS SPICE市場の95%をターゲットにしているという。同社セールス/マーケティング担当バイスプレジデントを務めるKent Jaeger氏は、「当社のマルチスレッド版SPICEである『Gemini』は、精度を落とすことなく2〜10倍の性能向上を実現する。(当社の設計者には)精度を落とす可能性のある手法を用いることを禁じている」と語る。

Geminiは、多くのベンチマークテストにおいて、高速MOS SPICEシミュレータよりも良い結果を出している。低コストの米Intel社製マルチコアプロセッサと64ビット対応のLinuxの組み合わせをサポートする。

■Infinisim社

米Infinisim社のCTO(最高技術責任者)を務めるZakir Syed氏によると、同社は精度を維持しつつ、高速SPICEでよく用いられる手法の一部を採用しているという。同社のシミュレータ「RASER」は、ブロックレベルからフルチップに至るまで、またプリレイアウト、ポストレイアウトを問わず、設計検証のすべてのレベルに対応する。同社マーケティング担当シニアディレクタのAnand Iyer氏によると、「RASERは、システム全体のシミュレーションを実施したいという重要な要求に向けられたものだ」という。

Iyer氏によれば、「素子数が数十万個を超えると、従来のSPICEシミュレータでは歯が立たなくなる。並列処理を行っても、あるレベル以上に能力を向上させることはできない」という。そこで、高速SPICEで用いられるのと近い手法が必要となる。Syed氏は、「高速SPICEと同様に、(回路を)より小さなパーティションに分割し、パーティションごとに異なるソルバーを適用する。その上で、SPICEで使用するのとまったく同じデバイスモデルを使用する」と述べる。

Infinisim社はマルチスレッドをサポートしており、なおかつ個々のスレッドの高速化にも取り組んでいる。Syed氏は、「例えば、モンテカルロ解析のように、マルチスレッドや分散コンピューティングの利用が可能なケースもある。このようなケースについては、シミュレーションの一部をほかの部分とは独立して実行することができる」と語った。

■Tanner EDA社

米Tanner EDA社の製品管理担当ディレクタを務めるNicolas Williams氏は、「アナログ設計においては、通常5つのコーナーモデルと温度スイープを条件としてシミュレーションを繰り返す。モンテカルロ解析を行いたい場合は、1つの回路に対し数千回ものシミュレーションを実行しなければならない。こうしたシミュレーションは、コマンドを使って、容易に分散して実行することができる」と述べる。「回路レベルではなく、シミュレーションジョブのレベルであれば、並列化による効果は大きい」と同氏は付け加えた。

Tanner EDA社のシミュレータ「T-Spice」は、アナログ回路が多く、デジタル回路の少ないチップの設計をターゲットとしている。同社は、ビヘイビアモデルとデバイスレベルのSPICEモデルの両方のシミュレーションに対応するために、Verilog-Aを採用することにした。

Verilog-Aは、トップダウン設計をサポートする。これにより、アナログ設計者が古くから用いているボトムアップ手法と比べてかなりの利点が得られる。Williams氏は、「設計フローの終盤において、システムの統合にかかわる問題が生じるケースがある。その場合、ボトムアップ手法では、設計のやり直し/繰り返しが発生する恐れがある。トップダウン設計であれば、その時間のかかる作業をなくすことができる」と述べる。

同氏は、「アナログ設計者は、ビヘイビアモデル手法を採用した設計も行う。また、定数計算などに米The MathWorks社の『MATLAB』を使用するケースもあるだろう。ただ、SPICEプログラミング環境内で使用できるビヘイビア言語は存在しなかった」と述べる。SPICEとビヘイビアモデルの組み合わせにより、設計者は長い実行時間をかけることなくシミュレーションを行えるようになる。

表1は、PLLのシミュレーションにかかる時間をCPUの占有時間を元に相対的に比較したものである。PLLの各構成要素について、SPICEモデルとVerilog-Aモデルをさまざまに組み合わせることによって、どの程度の差が生まれるのかが見てとれる。

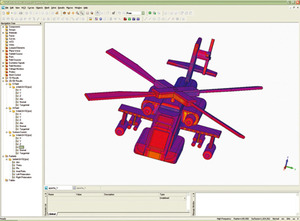

基板からヘリコプターまで

製品の複雑化/高速化が進むに従い、EMC(電磁環境適合性)/EMI(電磁波干渉)の影響をシミュレーションし、シグナルインテグリティ/パワーインテグリティについて検討することがますます重要となる。そのためのツールとしては、2D/3Dシミュレーションをサポートし、時間領域と周波数領域における表皮効果(Skin Efect)を解析可能な「PCB STUDIO」などがある。これは、ドイツComputer Simulation Technology(CST)社の製品であり、IBIS(I/O Buffer Information Specification)モデルを取り込んで、SPICEをはじめとする各種ツールとのやり取りが行える。同社の「Cable Studio」とともに、基板やケーブルの協調シミュレーションをサポートする。

CST社は、電磁界シミュレーションソフトウエア「Studio Suite 2009」にPCB StudioとCable Studioを統合している。自動的に最適化を行い、問題に対する最適なソルバー技術を適用することにより、設計スループットの改善を支援する(画面B)。Studio Suite 2009は、過渡的に変化する電磁界と回路協調シミュレーションをサポートし、64ビットシステムとMPI(Message Passing Interface)ベースの並列処理により、大規模で複雑な構造のシミュレーションを高速に実行する。また、加熱プロセスをシミュレーションするための過渡熱ソルバーも備えている。さらに、生理的冷却効果を現実的にモデル化するためにバイオ熱方程式を採用している。

Copyright © ITmedia, Inc. All Rights Reserved.