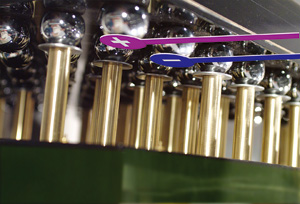

写真1はFPGAパッケージのコーナー(角)部分を模式的に表したものである。現実に見えるとおりを示しているわけではなく、プリント基板(プリント配線板)の部分を透明にし、同基板の下部層に接続するビアが見えるようにしている。この写真のとおり、はんだボールは、FPGAパッケージの下面に形成されている。

FPGAパッケージの内部には、インピーダンスを適切に制御した配線パターンが多数張り巡らされている。もう少し詳しく言うと、これらのパターンはFPGAパッケージ内部にあるBGA(Ball Grid Array)基板上に形成されている。それらのパターンにより、チップ上の回路がパッケージ下部のはんだボールに接続される。BGA基板には、通常のプリント基板と同様に“ベタ”の電源層とグラウンド層が複数形成されている。

写真1において、ピンクと青の部分は、隣接する2個のボールから引き出された差動信号線である。これらの差動信号線は、プリント基板の第1層に配線パターンとして形成されている。この写真は第1層の下側にある誘電体層を透明にしたものなので、2本のパターンの下面がパッケージから引き出されたリード線のように見えているということである。

ボールが形成された部分は、遷移領域である。差動信号は、この遷移領域を経由して、BGAパッケージ内部の微細なパターンからプリント基板の第1層にあるサイズの大きなパターンに引き渡される。遷移領域における差動インピーダンスは、主として信号の出口になる2個のボールの寸法と、2本のパターンの寸法、プリント基板のベタ基準面との距離に依存する。

写真1の構造は、BGAパッケージからプリント基板まで差動信号を引き出す方法としては最も望ましいものである。その要点は、すべてのパターンが短く形成されており、基準面に対して対称性を持っていることだ。プリント基板の第1層に差動パターンがあるので、同パターンには、ドリル穴やビアが必要なく、伝送条件が複雑にならなくて済む。

信号がパッケージ本体やコネクタ、あるいはビアを通過するケースを考える。そうした遷移領域がどのような構造であろうが、ある条件を満たせば、その領域を、簡単な近似によって等価回路に置き換えることができる。必要になる条件とは、その遷移領域で発生する遅延時間を、ドライバ回路による信号の立ち上がり/降下時間よりも十分に小さくすることである。この条件が満たせれば、信号には、その遷移領域内に存在する細かい構造の変化を平均化したものが影響として及ぶだけである。

ここでいう近似とは、具体的には、遷移領域を短い差動伝送ラインで置き換えることである。その特性インピーダンスZ1は、周辺の伝送線路の特性インピーダンスZ0とは異なる値になる。このような置き換えを行うことにより、短い不完全な部分の特性を、その部分全体を平均化したものとして表現できる。その領域内の不完全性は、領域内の1点に、全体の不完全性を打ち消す要素を追加することで相殺することができる。

文章で表現すると難しい話にも聞こえるが、具体的な対処はシンプルなものである。例えば、ボールの間隔が広すぎると、(インダクタンスが大きくなるので)Z1が過大になる。その場合、BGAのはんだパッドのサイズを大きくして容量値を少し増やしてやればよい。そうするとZ1が小さくなり、正しく補償されたものになるということである。このように、遷移領域で発生する問題点を十分小さな領域内で補償してしまうことが、遷移領域をうまく設計するコツだ。

ただし、この設計法は、遷移領域全体での遅延時間が、信号の立ち上がり/降下時間の約1/10以下に収まっている場合にしか有効ではない。遷移領域での遅延時間が信号の立ち上がり/降下時間の1/10を超える場合には、遷移領域をさらに細かく分割する。その上で、各部分がこの1/10の原則を満たすよう、各部分ごとに特性インピーダンスを補償すればよい。

<筆者紹介>

Howard Johnson

Howard Johnson氏はSignal Consultingの学術博士。Oxford大学などで、デジタルエンジニアを対象にしたテクニカルワークショップを頻繁に開催している。ご意見は次のアドレスまで。www.sigcon.comまたはhowie03@sigcon.com。

Copyright © ITmedia, Inc. All Rights Reserved.