リーク電流は「暗号」まで漏らす?:微細化にはセキュリティ低下の懸念あり(2/2 ページ)

ハッカーがセキュリティを破る手法の1つに、暗号化回路に用いられる各種デバイスの電気的動作など、ハードウエアレベルの物理的な現象を利用する「サイドチャンネル攻撃」がある。このサイドチャンネル攻撃の中でも、半導体チップのリーク電流を利用する手法に対し、憂慮の声が挙がっている。本稿では、微細プロセスで増大するリーク電流を測定/解析することで、暗号化回路の秘密鍵に関する情報が読み取られる可能性について考察する。

傾向に温度依存性はなし

筆者らは、標準的なCMOSゲートにおける入力値に対するリーク電流の依存性を把握するために、スイスSTMicroelectronics社の90nmプロセス向けライブラリ「CMOS090」のスタンダードセルを使ってシミュレーションを行った。そのシミュレーションでは、米Cadence Design Systems社の回路シミュレータ「Spectre」向けのモデルを使用した。

また、リーク電流の温度依存性を検証するために、5種類の温度設定でシミュレーションを実行した。そして、リーク電流と温度の関係を調べたところ、リーク電流の量自体は温度によって異なるが、入力値に対する傾向は変わらないことがわかった。例えば、2入力のNANDゲートでは、どの温度でも、それぞれの入力が「0」と「1」である場合のリーク電流が最も大きくなるといった具合である。このような傾向を基に、暗号解析は、暗号化コアにおけるリーク電流が最大または最小となる入力値の組み合わせを利用して行われる。

対称鍵方式の暗号化アルゴリズムで一般的に利用されているのが、Sボックス(Substitution Box)と呼ばれる関数である。ブロック暗号においては、Sボックスを用いて入力文と暗号文の相関を判別できないようにする。Sボックスは、mビットの入力値とnビットの出力値の間の組み合わせマッピングを行う。

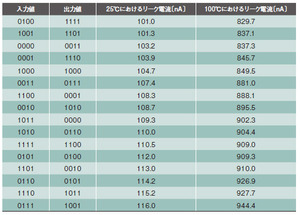

Cadence社の研究者らは、真理値表とSTMicroelectronics社の90nm CMOSプロセスライブラリを使って、4ビット入力/4ビット出力を持つ「蛇型」のSボックスを合成した。そして、考えられるすべての入力の組み合わせに対してリーク電流のシミュレーションを実施し、リーク電流が少ない順に入力の組み合わせを並べ替えた。その結果は、やはり温度に依存しなかった(表1)。この事実から、シミュレーションまたは測定において、熱係数(温度)が一定でさえあれば、暗号解析が実行可能であることがわかる。

Sボックスの入力にXORゲートを接続することにより、簡単な暗号化コアの組み合わせを再現することができる。XORゲートに任意の入力値と秘密鍵を混在させ、その次にSボックスにより暗号化した値を出力するというものである。図2に、4ビット入力/4ビット出力の暗号化コアを実現する回路を示した。緑色で示す部分に4個のレジスタ(Dフリップフロップ)を導入することにより、XORゲートを使った暗号化コアの回路を構成することが可能である。

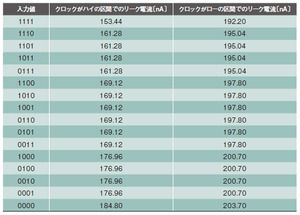

この回路に対し、すべての入力値、出力値、秘密鍵の組み合わせについて、網羅的にリーク電流のシミュレーションを行うことにより、リーク電流と暗号化コアとの相関を解析することができる。「0000」〜「1111」までの4ビットの数値で表される入力値に対して、4ビットの数値内にある「1」の個数とリーク電流との間に直接的な対応があることがわかった(表2)。この傾向は、クロックのハイ区間にあるか、ロー区間にあるかには依存しない。また、4ビットで表される入力値、出力値、秘密鍵のすべての組み合わせについてリーク電流を測定した。この結果、すべての組み合わせについて、リーク電流との相関が見られた。

相関係数を利用した攻撃

ハードウエアレベルの攻撃には、受動的なものと能動的なものがある*10)。受動的攻撃とは、暗号化を行う際に変化する何らかの物理的な値を測定することで収集できるサイドチャンネル情報を利用するものである。一方の能動的攻撃は、誤った演算を引き起こす障害を与え、秘密鍵の漏えいを導くものだ。

受動的攻撃において利用される最も一般的なサイドチャンネル情報が、半導体チップの消費電力である。その解析手法としては、単純電力解析(SPA:Simple Power Analysis)、差分電力解析、および相関電力解析(CPA:Correlation Power Analysis)などが挙げられる*11)。単純電力解析を用いる攻撃では、消費電力の変化を直接解析して得られるサイドチャンネル情報から、秘密鍵全体またはその一部を特定する。差分電力解析と相関電力解析は、統計的な手法であり、多くの測定値とデータ取得が必要となる。相関電力解析を用いる攻撃では、データ収集後に、収集したデータを解析し、攻撃対象の半導体チップに関する仮説モデルを適用する。

暗号化コアの秘密鍵を解読するために、統計的解析ツールが用いられる。また、取得したリーク電流に対応する入力値と、秘密鍵の仮説モデルを用いたロジック値との間の相関係数を計算する手法を攻撃に利用するケースもある。この手法では、Sボックスへの入力のハミング重み(入力値における「1」の個数)をロジック値として用いる。

これらの基礎的な研究により、リーク電流を利用することで秘密鍵の解読が現実的に可能であることが示されている。特に、相関係数を利用する攻撃は、90nm以下のプロセスを用いたリーク電力の大きい半導体チップにおける暗号化コアの設計でより重要な課題になり得ることを、各種の研究結果が示唆している。

脚注

※10…Jovanovic, Milena, and Z Mijanovic, "Leakage Analysis Attacks for CMOS Cryptographic Hardware and TDPL Technology as Countermeasure," Yuinfo Conference, 2007

※11…Jovanovic, Milena, "DPA Attack on FPGA Implemented Cryptographic Core," VIPSI Conference, July 2008

Copyright © ITmedia, Inc. All Rights Reserved.