プリント基板のアクセシビリティを高める:検証/デバッグを容易化するために(2/3 ページ)

プリント基板の検証やデバッグが非常に困難な作業となってきている。部品の高密度実装や、やりとりする信号の高速化が進んでいるからだ。こうした状況に対応するために、プリント基板を開発する際には、検証やデバッグの作業を容易に行えるよう、アクセシビリティを高める工夫を盛り込むことが求められている。

CATEGORY 1:電源とクロック信号

一昔前の設計検証技術者にとって、電源とクロックは、「信号が存在するか、仕様の範囲内か」という簡単な問いに答えられればよいだけの存在だった。各電源電圧を観測するために、最大負荷の近くのむき出しの配線と、電流を測定するための直列抵抗、各クロック信号を観測するためのむき出しの配線があればよかったのである。また、基板上で高速なクロック信号が分岐配線されることなどなかったので、スキューについて心配する必要もなかった。

ただ、簡単な基板上でも、電源ラインには細心の注意を払ってプローブを当てる必要があった。米Integrated Device Technology(IDT)社のテスト技術者であるRichard Fellner氏は、「どのような基板においても、グラウンドは低周波のノイズ源となる」と警告する。プローブとそのグラウンドをどこかに接続する前に、グラウンドプレーンにおけるコモンモードノイズの可能性について十分に検討しなければならない。

また、クロック信号のプローブにも注意が必要である。米National Semiconductor社でアプリケーション担当ディレクタを務めるRobbie Shergill氏は、「明らかに、測定による影響を与えてはならないクロック信号が存在する。例えば、高速なA-D/D-Aコンバータに供給されるクロック信号にプローブを当ててはならない。そのクロック信号を観測するには、バッファを用いて“複製信号”を用意し、それにプローブを当てて測定する必要がある」と述べる。

今日では、電源管理の手法としてクロックゲーティングやパワーゲーティングが用いられるようになった。これら技術の出現により、状況はさらに複雑になった。実際、積極的な電源管理により、電源やクロック信号は、一種のアナログ信号として扱うべきものとなった。検証技術者はクロックドゲートが動作しているはずの場合にのみ、チップにクロックが供給されていることを確認する必要がある。また、クロックゲーティングのモード間で遷移が生じる際、グリッチが生じないことも確認したい。あるいは、パワーゲーティングにより、SoCへの電源のオン/オフが正しいシーケンスで行われていることを確認しなければならない場合もある。このような要件から、電源/クロック信号について、基板には従来以上のアクセシビリティが求められる。

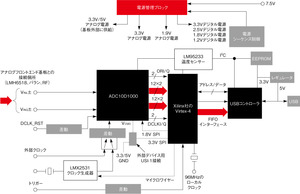

基板設計者は、基板上に10種もの電源電圧が存在する状態で、電源とクロック信号が正しいシーケンスによってアクティブになっていることを確認できるように、十分なアクセシビリティを提供しなければならない(図1)。これを実現するのは、簡単なことのように思えるかもしれない。しかし、例えばFPGAのコア電源端子とPOL(Point of Load)レギュレータの間に十分な空間がない場合、上述したアクセシビリティを提供するのは非常に難しい。基板設計の担当者に、「FPGAのすぐ横にレギュレータを配置するように」と指示しただけだと、そのような状況に陥る可能性が高いだろう。

基板で実行される機能を理解し、それを検証するために必要な測定方法の計画を立てること。これが常に従うべき原則である。IDT社のFellner氏は、「どの計測機器を使うのかといったことも含めて、テスト手法を定義しておく必要がある。その情報により、基板上に設けるべき接続方法の種類が決まる」と指摘している。

CATEGORY 2:アナログ信号パス

アナログ信号パスに対しては、電源/クロック信号へのアクセスと同様の考え方で対処することになる。信号パスの動作を理解し、信号パスの制御/観測のために必要となるノードを特定して、観測/測定に必要な手段を理解して提供すればよい。文章で書くと単純だが、これには多くの回路を解析した上で、どのように信号パスにアプローチすればよいのかを理解することが必要となる。また、高電圧プローブからRF回路アナライザに至るまで、あらゆる測定手法を理解することが要求される。National Semiconductor社のShergill氏は、「多くの場合、観測すべき信号は明白だ。問題となるのは信号パスであり、配線のどこで信号を観測する必要があるのかを検討しなければならない。端子へのアクセスが可能であればありがたい。だが、リファレンスデザイン基板を最終製品にできるだけ近いものにしなければならないことから、基板上では端子へのアクセスが難しい場合もある」と述べている。

Shergill氏は「幸い、1つの信号にアクセスできる場所が複数あるケースが多い」とも指摘している。ただし、物理的にアクセス可能かどうかだけが問題となるわけではない。プローブを当てることの影響を受けやすいため、観測が困難なノードも存在する。「アナログ信号の場合、ハイインピーダンスであるために、チップ内のリークだけで影響が生じることがある」と同氏は警告する。そのような信号にはプローブを当てることはできない。

プローブを当てられない場合、テストポイントで元の信号を複製しなければならないかもしれない。つまり、信号の観測用に部品を追加しなければならないことがある。実際、IDT社のFellner氏は「ほとんどの場合、われわれは一部の信号へのアクセシビリティを改善するために、基板上に部品を追加している」と述べている。その上で、同氏は「どうせ信号をバッファリングしなければならないのだから、基板レイアウトの任意の個所ではなく、デバッグしやすい個所をテストポイントにするのが1つのコツだ」とアドバイスしている。加えて、同氏は「アクセシビリティを設計する」という表現でその重要性を強調した。「単にテストポイントを設置するだけでは十分ではない。簡単な計算によって、何が必要なのか理解できる場合もあれば、シミュレーションの実行が必要な場合もある」(同氏)という。一方、米Ambarella社で大規模統合担当バイスプレジデントを務めるChan Lee氏は、「アクセシビリティの設計手法は、経験によって習得するものだ」と述べた上で、「その設計には、簡単な計算を利用する。正確なシミュレーションを行うには変数が多すぎる」と説明した。もちろん、検証/デバッグ担当者が行う必要のある測定の種類、使用する必要のある計測機器なども考慮に入れなければならない。

アナログ信号の観測は難しい作業だが、制御はさらに困難である。信号源を基板の外部に置く場合、信号パスを駆動するための適切な回路と信号生成器を使用することになるだろう。信号源が基板上のICに集積された熱センサーのようなものであるならば、さらなる検討が必要となる。おそらくは、外部リファレンスと多重化するためのアナログスイッチを使用することになるであろう。信号源がD-Aコンバータであるならば、その入力デジタルデータを観測する方法を検討すべきケースも多い。

CATEGORY 3:高速シリアルI/F

高速シリアルI/Fの入出力信号は、プロービングが非常に困難である。Ambarella社のLee氏は、「われわれは通常、MIPI(Mobile Industry Processor Interface)やLVDS(Low Voltage Differential Signaling:低電圧差動伝送)など、複数のイメージセンサー用I/Fを基板上に搭載する。これらのI/Fの中には、テストポイントでのスコープによる観測が可能なものと不可能なものがある」と説明する。

信号の高速化に伴い、問題はさらに深刻化している。IDT社のFellner氏は、「高速I/Fの中には、3GHz以上の差動信号を伝送するものがある。そのようなI/Fには、観測可能なポイントがない。アクセスが必要ならば、差動リピータを設計しなければならない」と指摘する。加えて、信号にアクセスできるようになったとしても、その解析は困難だ。「その信号は非決定的なものなので、従来の自動テスト装置では対処できない。データを復元するために、対応するレシーバが必要になる」と同氏は述べる。

このような高速シリアルI/Fへの対処法は、デジタル回路を開始点とするアナログ信号への対処法に似ている。ソフトウエアによってI/Fのデジタル終端を制御することができれば、かなり都合が良い。「ホスト上のソフトウエアにより、高速I/Fを制御する方法を採用することが多い」とLee氏は述べる。

通常、ソフトウエアによる制御は、バスにデータパターンを印加する機構とI/Fが自己チェックを行うためのループバック機構によって実現される。しかし最近では、多くの高速I/Fが提供するプログラマブルな電気特性を利用する手法も増えてきた。高速シリアルI/Fでは、シンプルなチップでも、スルーレートと駆動能力がプログラマブルになっていることがある。より高度なトランシーバでは、プリエンファシスとイコライゼーションがプログラマブルで、自動トレーニングシーケンスも提供されている。これらの機能の本来の目的は、トランシーバを基板上の条件に適応させることだが、このプログラマビリティを、特性評価の目的で用いたり、高速シリアルI/Fにプローブを接続した後でトランシーバを再調整したりするのに利用することも可能なのだ。

Copyright © ITmedia, Inc. All Rights Reserved.