半導体IPの検証手法:コンプライアンステストだけでは不十分!(2/2 ページ)

標準規格にのっとった機能を実現する半導体IPは、当然のことながらコンプライアンステストに合格していなければならない。しかし、実際にIPの品質を完全に保証するには、それよりもはるかに困難な作業が必要となる。

デジタルIPの検証

PCIeを例にとると、合成可能なデジタルIPとミックスドシグナルPHY IPの両方に対し、検証を実施する必要がある。ここでは、まずデジタルIPの検証について説明する。

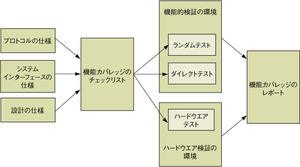

デジタルIPに対しては、機能カバレッジのチェックリストの作成から開始すべきである(図3)。検証技術者は、プロトコル、システムインターフェース、設計の各仕様を解釈してチェックリストを作成し、このチェックリストを前提として検証プロセスを決定する。

通常、機能的正確性の確認には、シミュレーションや、アサーションの記述、エミュレーション、ハードウエアプロトタイピングなど、複数の手法を組み合わせることが必要になる。シミュレーションを行う際、検証技術者はコードカバレッジを最大化するために、ランダムテストやダイレクトテストを実施する。ダイレクトテストは、ブロック内の機能を対象とし、コンプライアンステストに対応したカバレッジテストを含めて実施される。しかし、デバイスのすべての機能を網羅するわけではないことが多い。検証チームは、制約付きランダム検証手法と、仕様から導いた機能カバレッジポイントを使用することにより、ランダムテストにおいて、ほぼすべてのコーナー条件を網羅して完全に検証が完了するまでIPを系統的に動作させる。この手法では、検証カバレッジポイントを機能カバレッジのチェックリストおよび主要な仕様に照らし合わせて、進捗レポートを作成することができる。機能カバレッジのチェックリストとレポートは、機能的正確性を表す主要な指標であり、IPが回路内で正しく動作することを保証するのに役立つ。

筆者が所属するSynopsys社を例にとると、ダイレクトテストおよびランダムテストをIPに適用し、リグレッションテストのシミュレーションを毎日350億〜400億サイクル実行している。そのためには、常にリグレッションテストを実行するCPUが約500個も必要となる。そういう意味で開発側の負担は大きいのだが、このプロセスにより、IPの機能的正確性が保証される。また、どのようなツールチェーンを使用しても、IPベンダーで得られたのと同じ結果が得られることを顧客に対して保証できる。従って、完全な検証プロセスには、さまざまなEDAツールを用いてIPを徹底的にテストするフローと、複数のベンダーが提供する主要なシミュレータによるテストが含まれることになる。

何億サイクルものシミュレーションを実行したとしても、そのIPは実際のアプリケーションで動作させてみる必要がある。例えば、複数のPCIeインターフェースがあったとして、それらが同じ仕様に基づいているとしても、そもそも仕様のある部分が完全に定義されていなかったり、設計者によって解釈が異なったりする可能性があるからだ。このことが原因で、相互運用性の問題が発生することになる。

IPベンダーは、開発したIPを何らかのハードウエア(通常はFPGAプロトタイプボード)に実装してテストを行う必要がある。Synopsys社の場合、通常、そうしたハードウエアによる検証とコンプライアンステストの両方に、同じFPGAプロトタイプを使用する。そのため、FPGAを利用して、テストを追加したり、ほかのPCIeシステムやテスト装置との間で「PlugFest」などの相互運用性テストを実施したりすることが可能である。

残念ながら、IPベンダーがそのIPで実現可能なすべての構成をFPGAプロトタイプに取り入れることは困難である。従って、IPベンダーには、FPGAでテストした構成だけでなく、ほかの顧客が実際にシリコンチップに実装して量産に用いた構成について尋ねてみるとよい。

ミックスドシグナルIPの検証

上述したように、合成可能なデジタルIPには、多くの検証上の課題が存在する。アナログ/ミックスドシグナルのPHY IPでは、それとは別の種類の問題が生じる。65nm以下のプロセスノードのPCIe PHYには、いくつかの興味深い傾向がある。その多くは、物理的設計に依存して起きるものだ。

アナログ/ミックスドシグナルのPHY IPでは、デバイスサイズの違いによって生じるばらつきが大きな問題になる。このばらつきを予測するには、閾(しきい)値電圧とドレイン‐ソース間飽和電流の不整合に対するモンテカルロシミュレーションが必要となる。そのためには、膨大な計算時間と多くのツールのライセンスを要する。

また、STI(Shallow Trench Isolation)ストレス、WPE(Well Proximity Effect:ウェル近接効果)、接触ストレスなどにより、多くのばらつきが生じる。さらには、NBTI(Negative Bias Temperature Instability:負バイアス温度不安定性)、HCI(Hot Carrier Injection:ホットキャリア注入)、EM(Electromigration:エレクトロマイグレーション)による時間依存のばらつきが生じる可能性もある。これらすべてのばらつきに対し、プリレイアウトでの寄生素子抽出パラメータを使用するシミュレーションでは、性能を正しく予測することができなくなりつつある。デバイスの性能は、レイアウトに依存するばらつきの影響を受ける物理的な要素に、ますます依存するようになってきているからだ。そのため、ポストレイアウトで寄生素子抽出を行おうとする動きが加速している。

上述したようなばらつきのすべてが、プロセスコーナーを生成する。しかし、モンテカルロシミュレーションと同様に、すべてのプロセスコーナーにわたってミックスドシグナルIPのシミュレーションを実施しようとすると、かなりの演算能力が必要になる。

例えば、Synopsys社のIP製品ライン「DesignWare」に含まれるPCIe PHYを検証するためのシミュレーションでは、14の基本アナログブロックを対象とする。1ブロック当たり平均18個のテストベンチが必要になるため、テストベンチの合計は250個にも上る。ベンダーは、IR(電流‐抵抗)ドロップ効果を含めて、さまざまなプロセス/電圧/温度のコーナーに対し、各テストベンチを実行する必要がある。各テストベンチには、薄型/厚型ゲートデバイス、ポリシリコン抵抗、容量、その他の変数に対するそれぞれ独立したコーナーも含まれる。これらの項目をすべて合わせると、各テストベンチを平均90コーナーで実行しなければならないことになる。つまり、PCIe PHYの検証プロセスでは、この部分だけで、約2万3000回のシミュレーションが必要となるのである。

さらに、ベンダーは、歩留りなどを評価するために、従来のコーナー解析に加えてモンテカルロシミュレーションも実施するケースがある。すべてを合わせると、DesignWareのPCIe PHYの場合、総シミュレーション実行時間は約3.25CPU・年となる。

そして、シミュレーションの後には、信頼性の解析も行わなければならない。ポストレイアウトの寄生素子抽出シミュレーションにおいて、電力ネットと信号ネットの両方に対し、EMの影響について解析を行うベンダーもある。

オンチップでの工夫

高速PHY IPの性能は、予測が困難な複数の要因の組み合わせに依存する。そのため、膨大な解析を行うだけでは不十分であるかもしれない。すなわち、ミックスドシグナルIP向けのいくつかの新しい手法が必要となる。例えば、オンチップのサンプリングスコープとオンチップのプロセスモニターを使用するといった具合である。

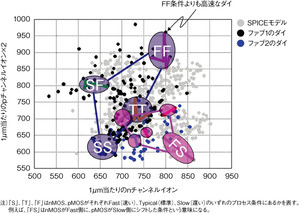

サンプリングスコープを用いれば、PHYチップ内の信号について把握することができる。すなわち、パッケージやボードの影響に依存しない性能を知ることが可能である。一方、プロセスモニターを利用すれば、ほかの手段では取得が困難な情報である、チップ上のコーナーの組み合わせについて把握できる。例えば、SPICEモデルからのデータと、2つの工場(ファブ1、ファブ2)で製造したチップのプロセスモニターからのデータとを比較すると、プロセス条件におけるどの位置にダイが存在しているのかという情報が得られる(図4)。この情報から、各プロセスコーナーに対応するダイを選択し、歩留りの予測などに生かすことが可能になるのだ。

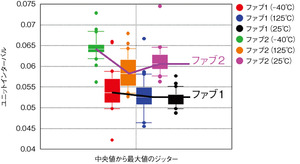

またこの機能によって、より有意義なジッター解析などが行えるようになる(図5)。ジッターによって歩留りが制限されるため、チップの性能は、定められた規格値を上回っていなければならない。すべてのダイがpチャンネル、nチャンネルともに遅いコーナーにあったとしても、この設計で正しく動作するのだろうか――この問いに対する答えは、オンチップのプロセスモニターがなければ知ることは実質的に不可能だ。

優れたSPICEモデルが得られる前でも、オンチップモニターからの情報を使用することで、アナログブロックのプログラマビリティを活用することができる。例えばPHYチップにおいて、ブロックの高速化/低速化を目的として、DCレベル、クロスオーバーポイント、立ち上がり/降下特性を調整するといったことが行えるかもしれない。プロセスモニターによって各ダイのコーナーの組み合わせを知ることにより、正確かつ効率的にプログラマブルなPHY IPの特性を設定することが可能になるのだ。

最良の設計/検証手法を適用したIPを使用すれば、正しく動作するチップを実現できる可能性が高くなる。それに加えて、ミックスドシグナルIP向けのオンチップ機能など、より高度な機能を導入すれば、市場における多種多様なベンダーとの明確な差異化を図ることができる。コンプライアンステストに合格することは必要条件だが、それだけではIPの品質を保証するのに十分ではない。設計/検証上のベストプラクティスを調査することも必須である。デジタルIPについては、機能検証計画とチェックリストが鍵となる。ミックスドシグナルIPについては、堅牢な設計やマージンの確保に向けた開発手法と、高い歩留りを実現するための明確な手法が重要である。

Copyright © ITmedia, Inc. All Rights Reserved.