SoC(System on Chip)では、コア用とI/O用の2種類の電源が使われる。正常に起動するには、個々のSoCの電源シーケンスの規定に従って、一方の電源が完全に立ち上がってから他方の電源を投入する必要がある。通常はコア用の電源を最初に立ち上げ、次いでI/O用の電源を起動することになるであろう。本稿で紹介するのは、このように電源電圧を直接制御するのではなく、システムリセットを制御することでSoCを正しく起動する回路である。

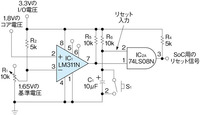

図1の回路は、コア電圧が1.8V、I/O電圧が3.3VのSoCを対象としている。コア電圧がI/O電圧よりも先に立ち上がった場合、SoC用のリセット信号として論理レベルのハイを出力する。また、I/O電圧が先に立ち上がった場合には、コア電圧が完全に立ち上がるのを待って、SoC用のリセット信号としてハイが出力される。

コンパレータIC1は、SoCのI/O電圧と同じ3.3Vで動作し、2つの電圧をモニターする。1つは1.8Vのコア電圧である。もう1つはI/O電圧だが、これについては、抵抗R2と可変抵抗R1によって分圧回路を構成し、コア電圧の立ち上がりが完了したか否かを判定するための基準電圧(1.65V)をIC1の3番端子に入力する。なお、プッシュボタンスイッチS1は、SoC用のリセット信号を強制的にローにするためのものである。

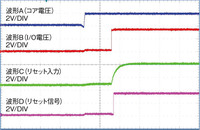

図2は、まずコア電圧(波形A)が立ち上がり、続いてI/O電圧(波形B)が立ち上がる場合の動作波形である。このケースでは、コンパレータIC1はI/O電圧が投入されるまでは動作しない。I/O電圧が投入されると、IC1およびANDゲートのIC2Aが動作を始める。IC1の2番端子(以下、+端子)の電圧が3番端子(以下、−端子)の電圧よりも高いので、コンパレータ出力(7番端子)のレベルがプルアップ抵抗R5を介してハイに引き上げられる。

IC2Aのリセット入力(波形C)は、最初はローレベルだが、I/O電圧の立ち上がりに伴い、抵抗R6を介してコンデンサC1が充電されるので、充電の進行に連れてレベルが上昇する。この充電のRC時定数は、実際の用途に応じて調整する。C1の充電電圧がハイの閾値レベルを超えると、リセット入力がハイになり、それに対応してIC2Aの出力(波形D)がハイになって、SoCがリセットされる。

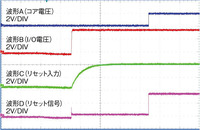

図3の電圧波形は、I/O電圧(波形B)が先に立ち上がり、次いでコア電圧(波形A)が立ち上がる場合のものである。この例では、コア電圧の立ち上がりが時定数R6×C1相当の時間だけ遅れるように設定した。コア電圧が0Vのときは、コンパレータIC1の−端子の電圧が+端子の電圧よりも高い。従って、コンパレータ出力はローになる。一方、ANDゲートIC2Aのリセット入力は、I/O電圧によるコンデンサC1の充電によってハイになり、そのまま保持される。このとき、SoC用のリセット信号(IC2Aの出力)はコア電圧が立ち上っていないのでローのままである。コア電圧が立ち上ると、コンパレータIC1の+端子の電圧が−端子の基準電圧よりも高くなる。その結果、コンパレータ出力がハイになる。リセット入力がハイであることから、ANDゲートIC2Aから出力されるSoC用のリセット信号もハイになる。これによりSoCがリセットされる。

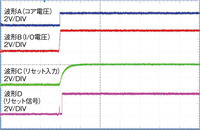

図4はI/O電圧(波形B)が先に立ち上がり、その後にコア電圧(波形A)が立ち上がるもう1つのケースの電圧波形である。この場合の動作は、コア電圧の立ち上がりの遅れがわずかであることを除き、図3と同様である。コンパレータの出力電圧は、コア電圧が立ち上がり、+端子の電圧が1.65Vを超えるとハイになる。しかし、SoC用のリセット信号がハイになるのは、コンデンサC1がハイレベルに充電されたときである。ハイレベルに充電されたら、ANDゲートIC2AからSoC用のリセット信号が出力される。

Copyright © ITmedia, Inc. All Rights Reserved.