A-Dコンバータを使用する際、データシートに記載された値でS/N比が得られるのを期待するのは当然のことだ。しかし、A-Dコンバータの使用条件として理想的な環境を実現するのは難しく、評価結果がデータシートに記載された値まで到達しないこともよくある。

A-DコンバータのS/N比に影響を与える要因としては、量子化ノイズ、非直線性誤差、A-Dコンバータ内部の等価入力ノイズ、クロックジッターなどがある。例えば、プリント基板のレイアウト設計が良好で、ノイズの少ない入力信号を使ったとしても、入力信号の周波数とクロック信号のジッターの関係によっては問題が生じ得る。クロック発生器の中には、1psのジッター性能を実現しているものがある。一方で、FPGAによって発生するクロックのように、良好であるとは言えないものも少なくない。A-Dコンバータを使用する際、1psといったジッター性能をうたうクロック発生器を使用すれば十分な性能が得られることが多い。しかし、入力信号の周波数が高く、高速なA-Dコンバータが必要となる場合に良好なS/N比を実現するには、クロック発生器として、より性能の良いものを使わなければならないこともある。

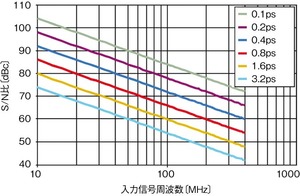

A-DコンバータのS/N比に対してジッターが問題になるかどうかは、次式を利用して評価することができる。

SNRCLK=−20log10(2πfIN×tJITTER-TOTAL)

この式において、fINはA-Dコンバータへの入力信号の周波数、tJITTER-TOTALは、クロック信号とA-Dコンバータのクロック入力回路とに起因するジッターの実効値(RMS値)である。ここで、fINはサンプリングクロックの周波数fCLKとは異なることに注意されたい。

1psという外部クロックのジッターは、A-Dコンバータの用途によっては問題のない値である。だが、この値は、あらゆる用途に対して十分なわけではない(図1)。上に示した式から、A-Dコンバータを使用する際に必要なジッター条件を概算することができる。例えば、A-DコンバータのS/N比として70dBが求められており、入力信号周波数が100MHzである場合には、tJITTER-TOTALは503fs(フェムト秒)となる。ここで、A-Dコンバータのアパーチャ時間のジッターをtJITTER-ADCとすれば、外部クロックに許容できるジッターtJITTER-CLKは次式で求めることができる。

tJITTER-ADCは、クロックの振幅とエッジの傾きに依存する値だが、ここでは、これらの影響が無視できるとしよう。そして、tJITTER-ADCの値が150fsであると仮定する。そうすると、上式から、tJITTER-CLKの許容値は480fsとなる。

ここまでに示したのは、高速A-Dコンバータ用のクロック信号に求められる要件の一端である。回路を設計する際、より詳細にはクロックの振幅やエッジの傾きについても十分に考慮しなければならない。さらに、ジッターの少ないクロック回路の構成法について理解しておくことも不可欠だ。

クロック信号源を設計する際には、A-DコンバータのS/N比に対するクロックジッターの影響が、クロックジッターと入力信号周波数に依存することに留意されたい。また、メーカーが提示するクロック発生器の仕様をうのみにしてはならない。製品開発にあたっては、A-Dコンバータのメーカーが供給する評価ボードを使用してクロック発生源を評価するとよい。そうすれば、製品仕様を満足する最終結果が得られるであろう。

<筆者紹介>

Bonnie Baker

Bonnie Baker氏は「A Baker's Dozen: Real Analog Solutions for Digital Designers」の著書などがある。Baker氏へのご意見は、次のメールアドレスまで。bonnie@ti.com

脚注

※1…Bartolome, Eduardo, et al., "Clocking high-speed data converters," Analog Applications Journal, Texas Instruments, First Quarter, 2005

※2…Sanna, Chuck, "Using high-IF sampling A/D converters beyond baseband frequencies," Planet Analog, Sept 5, 2007

※3…Wu, Lin, "Clocking a High-Speed ADC," Texas Instruments, 2008

Copyright © ITmedia, Inc. All Rights Reserved.