SoC vs.マルチチップ:「集積」と「分割」の正しい見極め(1/3 ページ)

1つのシステムを1つのICで実現――SoCのコンセプトは明解で、非常に魅力的なものであることに間違いはない。しかしながら、実際にはSoCのように、1つのICにすべてを集積することが最適であるとは限らない。複数のICに機能を分割し、マルチチップでシステムを構築するほうが、SoCを用いるよりも賢明な場合が少なからず存在するのだ。

SoCは常に最適な解なのか?

これまで、SoC(System on Chip)は、“電子部品の理想形”とも言える存在だった。機器設計者にとって、小さなチップ上に多くのデジタル回路を搭載し、機器を高機能化できることは大きなメリットだった。つまり、SoCは、より小さく、より高度な機能を容易に実現してくれる存在であった。だが、今日その状況に変化が訪れつつある。

SoCは、非常に多くのデジタル回路を搭載するために、最先端の微細プロセス技術で製造する。その微細プロセス技術はいくつかの問題を抱えている。1つは、最先端の微細プロセスはアナログ回路や電源回路、RF回路には適していないということである。また、微細なCMOSトランジスタは、ノイズやリーク電流の問題を生じやすい。さらに、そのフォトマスクのコストは、100万米ドル(約1億円)以上にも達してしまうことがある。このことは、そのコストを償却できる分だけ大量に製品を販売するまでは、設計を変更できないということを意味する。

以上のような問題があることから、SoCを選択するよりも、複数のチップに分割したマルチチップ構成で機能を実装するほうが有利なケースが存在するのである。

集積化の失敗例

従来は、集積度を高めることが進化の正しい方向性であるかのように考えられていた。しかし、歴史を振り返ってみると、集積化の戦略を大きく誤ってしまった企業がいくつもある。そのような企業の例として、米Trilogy Systems社が挙げられる。同社はメインフレーム全体を、単一のチップ上に集積しようと考えた。つまり、今日のSoCの前身に当たるものを開発していた。Fortune誌の元記者だったMyron Magnet氏によれば、「同社の2億3000万米ドルというベンチャーキャピタルファンドは、『新興企業としては過去最大の共同出資金』であった」という*1)。

Trilogy Systems社の開発したチップは、歩留りの問題から、誤り検出/補正用の冗長な回路を実装しなければならない状況に陥った。この問題によって結局破綻に至り、同社のチップはシリコンバレーの歴史における最大の失敗例となった。補正回路の増加に伴い、設計者らは、それらすべての回路をテストするのは不可能だという結論を下したのである。

このように、1チップで集積度を高めることが常に最良の選択肢であるわけではない。米Analog Devices社でアナログ技術担当バイスプレジデントを務めるDave Robertson氏は、やみくもに集積度を上げようとするのではなく、「スマートパーティショニング」を採用することを勧めている。つまり、機能を分割し、それらを複数のチップに分けるのだ。「個々の案件によって、最適な方法は異なるので、それぞれについて賢明な方法を選ばなければならない。2010年における賢明な方法は、2007年には賢明な方法ではなかったし、2013年の賢明な方法とも異なるだろう」と同氏は述べる。

プロセス技術の選択

米Texas Instruments(以下、TI)社でチーフテクノロジストを務めるTim Kalthoff氏は、「われわれは、まずどのプロセス技術が最も適切であるかを考える。その選択結果によって、チップを1つにするほうがよい場合と、マルチチップを使用するほうがよい場合に分かれる」と述べる。ここでは、プロセス技術を選択する際に考慮すべき事柄について述べる。

アナログ回路の場合、ロジック回路よりも多くのプロセスステップ数が必要になるケースがある。従って、アナログ回路は、分割が適している可能性がある。例えば、米Samplify Systems社は、データ圧縮機能を内蔵するA-Dコンバータを製造しているが、超音波装置用の低ノイズアンプのようなアナログ回路については、異なるプロセス技術を用いて別のチップとしている*2)。

米SiTime社は、最先端プロセス技術を用いたMEMS(Micro Electro Mechanical System)発振器を供給している。同社のMEMS発振器では、シリコン構造物を、シリコン酸化物、つまりガラス内部に配置し、さらにポリシリコンで覆い、ガラスをフッ化水素で溶解することによって、片持ち梁(かたもちばり)型の発振器構造を形成している*3)。このICは、信号調整などを行うための回路も集積している。しかし、このMEMS発振器をASICやFPGAに集積するというのは賢明な考え方ではない。もし、そのように集積を行うと、MEMS部分のために全体のプロセスステップが増えて、チップ全体のコストが大きく増加してしまうからだ。

また、MEMS回路やアナログ回路、メモリー回路などに必要となるプロセスステップを微細デジタル回路用のプロセスに付加すると、チップの歩留りは低下する。Robertson氏は、「確かに、われわれは、センサーと信号調整機能を同じシリコン基板に搭載したMEMS製品を供給しているが、センサーと信号調整器を分離し、単一のパッケージに2つのチップを搭載した部品も製造している」と述べる。つまり、コストと性能のバランスに応じた最適な手法を選択することが重要なのだ。

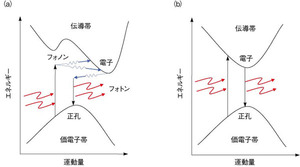

シリコントランジスタは、光トランジスタとしては最良のものではない。GaAs(ガリウムヒ素)などの直接バンドギャップ材料では、最大効率は41%にもなる。一方、シリコントランジスタの最大効率は、わずか22%にしか達しない(図1)。

この課題を解決するために、ゲルマニウム半導体とガリウム半導体の両方をシリコンチップ上に配置し、2つのプロセス技術を組み合わせようという研究が進められている*4)。しかし、この研究が実用化されても、SoCに適用されるような微細なプロセス技術に採用されることはないだろう。微細なプロセス技術に新たにプロセスステップを追加するのは経済的に不可能であるためだ。

光電子特性のほかにも、GaAs半導体には電子移動度が高く、バンドギャップが広いという特徴がある。つまり、RF回路に適している。一方、微細なプロセス技術を用いたSoCでは、RF回路部で必ずシリコントランジスタの特性に起因する問題が生じる。例えば、2.4GHzのWi-Fiホットスポット対応のチップには、ほぼ間違いなく微細CMOSプロセス技術が使用されている。だが、その種のICを2.4GHz以上の周波数で動作させると、線形性が低下して電圧範囲が狭くなってしまう。言い換えれば、アナログ回路として動作する余裕がほとんどないということだ*5)。このような制約があることから、多くの企業は2.4GHz以上で動作するようなRF回路には、CMOSプロセス技術ではなく、SiGe(シリコンゲルマニウム)プロセス技術を用いている*6)。

GaAsのほかにRF回路に適したプロセス技術として、SOS(Silicon on Sapphire)が挙げられる。水晶サファイア基板にCMOSトランジスタを形成するというものであり、例えば米Peregrine Semiconductor社が製品化を実現している。SiGe系/GaAs系のICより低コストで同等の性能を達成できるというが、そうは言っても、SOSのウェーハはバルクシリコンと比べれば高価である。

微細CMOSプロセスにおける酸化膜は薄いので、トランジスタを低い電源電圧で動作させる必要がある。デジタル回路の設計においては、この低い電源電圧という特性はメリットになる。電圧が低ければ消費電力も下がるからだ。しかし、RF回路では、このことはデメリットとなる。なぜなら、一般的なRF回路は、信号を無線で広範囲に発信する必要があり、微細なCMOSプロセス技術では使用できない高い電圧を取り扱うことを求められるからだ。

また、微細なCMOSプロセス技術には、リーク電流が多いという問題がある。リーク電流が問題になる回路については、絶縁分離されたシリコンプロセスであるSOI(Silicon on Insulator)を用いることで対処できる。しかし、この場合、微細なCMOSプロセス技術の最大のメリットであるコスト低減という利点が失われてしまう。

脚注

※1…Magnet, Myron, "Gene Amdahl Fights to Salvage a Wreck," Fortune, Sept 1, 1986

※2…Rako, Paul, "Diagnostic ultrasound gets smaller, faster, and more useful," EDN, June 25, 2009, p.21

※3…『発振器選択の手引き』(Paul Rako、EDN Japan 2009年6月号、p.30)

※4…Mehta, Rupal, "Novel technique developed to grow semiconductors on silicon," Materials World, Aug 31, 2007

※5…Rako, Paul, "Heads and tails: Design RF amplifiers for linearity and efficiency," EDN, April 2, 2008, p.31

※6…『SiGeが切り開く半導体の未来』(Paul Rako、EDN Japan 2009年7月号、p.38)

Copyright © ITmedia, Inc. All Rights Reserved.