SoC vs.マルチチップ:「集積」と「分割」の正しい見極め(3/3 ページ)

1つのシステムを1つのICで実現――SoCのコンセプトは明解で、非常に魅力的なものであることに間違いはない。しかしながら、実際にはSoCのように、1つのICにすべてを集積することが最適であるとは限らない。複数のICに機能を分割し、マルチチップでシステムを構築するほうが、SoCを用いるよりも賢明な場合が少なからず存在するのだ。

テストが重要な要素に

システム分割や回路設計などは、ICを顧客に届ける前に行わなければならない作業のほんの一部にすぎない。実に多くの作業が必要になるわけだが、特に製造工程で行うべき重要なこととしてテストが挙げられる。「テストの実施とそのためのテストシステムの設計が、IC開発における最大の作業かもしれない」と米Linear Technology社でスタッフサイエンティストを務めるJim Williams氏は述べる。安価なデジタルテスターでは、高性能のアナログICをテストすることはできない。そのため、テストの対象となるアナログIC用のプローブカードや測定器は、カスタマイズされたものであるケースが多い。

ある大手半導体企業は、最近になって、全製品のテストを標準的なデジタルテスターへと移行した。その際、アナログテストの難しさを痛感することになったという。高性能アナログ部門でプローブカードやテストルーチンを設計した社員はすでに定年退職していた。残されたドキュメントは乏しく、回路はデジタルテストのエンジニアが有する知識の範囲を超えた見慣れないものであった。すべてのICをデジタルテスター上で動作させるという作業は、同社が考えていた以上のリソースを費やし、悲惨な状況に陥った。

集積か分割かという判断は、テストについて考慮した上で決定しなければならない。安易に集積を進めると、Trilogy Systems社の二の舞になってしまうことを肝に銘じておくべきだ。

パッケージ技術の進歩

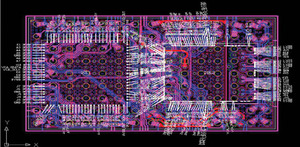

集積か、分割かを見極める際には、パッケージについても検討する必要がある。ICが40端子のセラミックパッケージで提供されていたころには、新たにICを追加すると、コストとプリント基板の面積がかなり増加してしまっていた。だが、現在ではICのパッケージのサイズを、チップのサイズとほとんど変わらない程度に抑えることが可能になった。多くのアナログ製品ベンダーが、チップスケールパッケージで製品を供給している(写真2)。

機能を別々のチップに実装して分割することで、個々のチップにおけるプロセス技術の選択肢のほかに、プリント基板上の実装位置にも柔軟性が生じる。また、それが設計目標を達成するための鍵となる可能性もある。これに関連して、多くの企業は、複数のチップを単一のICパッケージに収容することにより、上記の柔軟性とシングルパッケージによるサイズ縮小の両立を果たしている。例えば、TI社は医療用超音波装置向けのアナログフロントエンドICを製品化している。この製品は、2つのチップを単一のパッケージに収めたものとなっている。アンプ部については、低いノイズ性能を実現するためにSiGeプロセス技術を用いたチップを用いている。デジタル処理の機能やA-Dコンバータの機能は、コストや性能の観点から微細CMOSプロセス技術を使用したチップで実現している(写真3)。

Linear Technology社は、2つのデュアルオペアンプを同一パッケージに収めたクワッドオペアンプ製品を販売している。また、トランスや複数のチップを搭載したRS-485絶縁ドライバモジュールを開発している*8)。

同様の考え方で、Analog Devices社は、2つのチップとスパイラルトランスを1つのパッケージに収めたアイソレータを供給している。

「この10年間に、ICのパッケージ技術が進歩したおかげで、設計ルールがかなり変化した。さらに、今後の10年間で、スルーシリコンビアなどのパッケージ技術が再び設計ルールを変化させていくだろう」とRobertson氏は予想する。

変化への対応

これまで広く行われてきた議論において、賛否両論の意見が存在することから、集積と分割については、固定的な正解があるわけではないことがわかる。開発しようとしているシステムが、コストに対する消費者からの要求が厳しく、性能に対する要求がそれほど高くない確立された市場向けのものであるならば、微細なCMOSプロセス技術が最良の選択肢となる。しかし、確立されていると思われている市場にも変化は訪れる。例えば、先述したようにWi-Fi向けのICは微細プロセスによって1チップで実現するのが一般的である。しかし、今後、スパムや悪質なクラッカーを排除するために詳細なパケット検査を行う機能が必要になったとしたら、複数の小さな部品に分割しておくべきだったと後悔することになるかもしれない*9)。

また、フォトマスクのコストや製造プロセスの性能、設計作業の内容などは、日を追うごとに変化していく。従って、集積と分割のルールは、それを策定するタイミングによって異なるものとなるだろう。

アナログ設計を専門とする企業ならば、分割を選択したくなるケースが多々あるはずだ。しかし、競合他社は、同様の機能を1チップで実現しようとするかもしれない。どちらが良いかは、最終的には市場が決定することになる。いずれにせよ、システムを分割することのすべての意味を理解し、市場の違いや状況に応じて正解は異なることを把握しておかなければならない。

Analog Devices社のRobertson氏は、「だからこそ、この仕事は面白い。3年前と同じ問題に取り組んでいるとしても、“ツールボックス”が数年ごとに変化するので、問題に対する異なる対処法が出現する。設計上のトレードオフも変化していく」と語る。システムの分割は、現実世界における問題である。そして、現実世界は常にアナログ的なものだ。この事実から、集積と分割は非常に複雑な問題となる。それを解決できたときには、大きな達成感を得ることができるだろう。

脚注

※8…『「アイソレータ」を活用せよ!』(Paul Rako、EDN Japan 2010年1月号、p.22)

※9…Wilson, Ron, "Lessons from the last mile," EDN, Nov 26, 2009, p.18

Copyright © ITmedia, Inc. All Rights Reserved.