ICのアナログテストに新潮流は生まれるか?(2/2 ページ)

これまで、ICのデジタル回路をテストするための技術には高い関心が向けられてきた。実際、さまざまな新技術が登場したことで、デジタル回路の規模が爆発的に増加する状況にあるにもかかわらず、破綻を来すことはなかった。それに対し、ICのアナログ回路のテストについては、現在でも、革新的な手法は生まれていない。アナログテストにかかわるトータルのコストを下げる打開策は存在するのだろうか。

SERDESの事例

米Synopsys社のAMS IP担当製品マーケティングディレクタを務めるNavraj Nandra氏は、高速SERDES(シリアライザ/デシリアライザ) IPブロックの例を示してくれた。同社のようなIPベンダーは、AMS IP機能としてSERDESを供給していることが多い。この回路ブロックは、SoC内の並列データパスと、外部に通じる数GHzのシリアルバスの間の双方向インターフェースの役割を果たす。そしてSERDESの中心には、CDR(クロックデータリカバリ)回路が存在する。この回路は、入力信号からクロックを復元し、そのクロックを用いて信号からビットデータを抽出する。これらの機能を実行するために、CDR内の回路は、データストリームを生成したクロックを、局所的に生成されたクロックと突き合わせることにより、その位相を検出する。Synopsys社の設計では、デジタル制御の位相回転器によってこの処理を行う。

そして、この位相回転器には、もう1つの役割がある。テストモードにおいて位相を掃引し、CDR回路の出力をコンパレータでキャプチャすることにより、設計者は入力信号に対する位相と電圧の対応表を作成することができる。そのデータをチップからワークステーションへと送信し、グラフ処理を施すことによってアイダイアグラムを得ることが可能になるのだ。

多くのシリアルインターフェース規格では、アイダイアグラムの開口部に収まるポリゴンによって最小信号品質を定義する。そのため、Synopsys社のSERDESチップでは、内部のツールにより、このポリゴンに相当するコンプライアンスアイマスクを生成するために必要なデータを収集できるように設計してある。「この手法が、製造におけるテストルーチンの基礎にもなっている」とNandra氏は述べる。

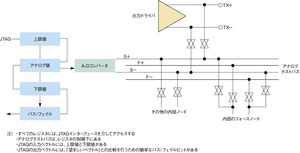

CDR回路の出力部にA-Dコンバータとリミットレジスタを配置し、サンプリングクロックを適切に制御してA-Dコンバータに供給すれば、データを収集し、外部ディスプレイルーチンに送信して、サンプリングオシロスコープと等価なものを構成することができる(図1)。このオシロスコープにより、アイダイアグラムだけでなく、A-Dコンバータの入力に供給する任意の繰り返し波形を観測することが可能になる。「顧客は、これらの機能を用いて、システム内で設計の接続性能を評価することができる」とNandra氏は語る。ここで示したのは、Synopsys社の設計者は、いくつかのハードウエアを追加するだけで、複数の顧客向けの複数の機能を実現しているという例である。

“アナログ版BIST”に向けて

上で例にとったSERDESは、テストモードにおける機能コンポーネントの再利用を可能にすることを念頭に実装されている。その手法は、実装に特化したものである。従って、別のSERDESを設計する際には、異なる手法が用いられるかもしれない。また、例えばΔΣコンバータの設計には、このSERDESで使用されている回路を直接適用することはできない。確かに、ウィジェットをチップに集積する手法は急速かつ広範囲に普及したが、再利用可能な計測回路のライブラリや、アナログ回路用の自己テスト機能の自動設計が普通に使われるようになるほどに広まっているわけではない。

米Mentor Graphics社に買収された米LogicVision社は、この問題に深く取り組んでいた。ITCのパネルディスカッションでは、LogicVision社の買収によりMentor社が手に入れた構想の一部が語られた。Mentor社のエンジニアであるStephen Sunter氏は、以下のように述べている。

「われわれは、アナログ回路において、スキャンに相当するものを探求している。しかし、必要なのは確立された故障モデルだ。単に、回路におけるランダムな欠陥を検出したいという希望と、高精度な特性評価の問題を切り離す必要がある。われわれは、これまで、広いダイナミックレンジを持つ複雑な波形に取り組み、複雑な解析も行ってきたが、いくつかの手法を使用するということで合意が形成できれば、新たな道に前進することが可能だと考えている。1つは、ループバックモードを使用すること。もう1つは、信号源からA-Dコンバータへのアナログ信号の伝送に、IEEE 1149.1に準じた低周波アナログバスを採用すること。最後の1つは、ΔΣコンバータからのデータの抽出に、高速シリアルバスを用いることだ。想定していることの基本原則は、電圧を時間へと変換することによって広いダイナミックレンジを管理し、作業の90%をデジタルの領域で行おうというものだ」。

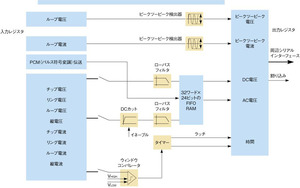

Sunter氏の構想は、SoCの分野で行われようとしていることと同様のものである。また、Synopsys社がSERDESの設計に用いている手法とも同じだし、Nuvoton社の戦略とも共通している。Nuvoton社のHemming氏は、「データシートに記載されたパラメータの特性評価を行うテストを高速化するには、内部アナログバスを用いて、アナログノードを高い精度で観測すればよい。しかし、この精度で十分だろうかという疑問が常について回る。また、われわれが対象としている市場ではコストが大きな問題になる。そこで、通常動作に使用する回路をテストに利用したり、顧客も利用できるようなテスト回路を設計したりすることを常に検討するようにしている」と述べる。Hemming氏は、同社の「Pro-X(Programmable Extended) CODEC」におけるやや規模の大きい電話回線測定機能を例にとり、上述した概念について説明してくれた(図2)。

オンチップ計測の利用が、Mentor社のSunter氏が提唱する一般原則のようなものに統合され始めているように思われる。しかし、オンチップ計測回路を設計に盛り込んだり、テストを自動生成したりするようなツールが登場するのは、まだまだ先のことになりそうである。

アナログ回路の構造テスト

確かに、オンチップ計測の手法は進化を遂げた。しかし、チップ上のアナログテスト用ウィジェットと、デジタルスキャン/BISTとの間にはまだ根本的な違いが存在する。アナログ計測回路は、ブロックの動作を測定するための場当たり的な手段としてブロックに手作業で挿入される。一方、デジタル回路用の自動化ツールは、ロジック構造の解析を行った後に、合成されたデジタルスキャンチェーンやBIST用のハードウエアを生成する。これらのツールは、設計における構造の整合性を検証するために用いられ、ロジック動作が正しいかどうかという検証には用いられない。

動作テストから構造テストへという流れにおいて、その中心となるのは故障モデルである。ウェーハ上でどのような欠陥が生じ得るのかがわかるなら、回路上の各欠陥の影響をモデル化し、1カ所のみを観測することによって、生じ得る問題のうちの多くを検出する方法を導き出すことができる。

デジタルの世界では、ATPGソフトウエア、スキャン挿入、DFTハードウエアを組み合わせ、生じ得るすべての故障を検出するために必要な最小数のテストを実施する。しかし、アナログの世界には、確立された故障モデルというものが存在しない。そのため、アナログ回路ネットワークから、回路全体の構造を実証することのできるパスやテストの最小集合を自動的に抽出する方法は確立できていない。

とはいえ、一縷の望みはある。それは、適応型(adaptive)テストを導入するという考え方だ。

適応型テストは、構造的な解析ではなく、統計的な解析に基づいたものである。適応型テストでは、製造ラインにおけるテストまでの間のすべてのテストデータを収集し、すべてのデータに統計的解析を施して以下のような判断を下す。例えば、テスト1で検出される故障がすべてテスト2でも検出可能であったとする。テスト2で、それ以外の故障も検出できるならば、適応型テストのプログラムでは、テスト1を削除し、テスト2を残すといった具合である。このように、適応型テストでは、故障モデルや回路構成に関する知識がなくても、原則的に必要最小な数のテストだけが残るまで、テストスイートの内容を絞り込むことができる。

ただし、その処理は非常に複雑である。自信を持って判断を下すには、膨大な量のデータが必要になる。発生がまれな故障を検出する唯一の手段であったテストを削除してしまうようなことは避けなければならない。Intersil社のPurtell氏は、「残念ながら、ほとんどのアナログ部品に対し、確信を持って判断するに十分な量のデータが得られることは、まずない」と述べている。

アナログ回路における適応型テストは、構造テストと同様に、まだ検討初期の段階にある。おそらく、どちらの手法についても、まだその可能性を見極めることはできない。誰かが明日、アナログ回路の強力な故障モデル集合を提案し、突然、構造的な手法が格段に魅力的なものとなるかもしれない。しかしそのような発見が、いつ訪れるかは誰にもわからない。

現在、IC業界は大きな問題に直面している。一部のテスト手法は、微細なプロセスノードで使用するにはコストがかかり過ぎるようになってきた。オンチップ計測は普及しつつあるが、そのための設計にはコストがかかり、精度の検証が必要となる。構造的な解析手法も統計的な解析手法も、さまざまな理由から、アナログテストにはまだあまり有効ではない。アナログテストは、容易な解決策がまだ見出されていない、重要な問題なのである。

Copyright © ITmedia, Inc. All Rights Reserved.