米Lattice Semiconductor社は2010年10月、ミックスドシグナルICの新ファミリ「Platform Manager」を発表した。電源管理やシステムのデジタル制御を行うための機能を1チップに集積したもので、同社の「Power Manager I」、「Power Manager II」に続く第3世代の製品となる。

同社でコーポレートマーケティング担当のバイスプレジデントを務めるDouglas Hunter氏は、「ミッドレンジのFPGA、低回路密度(ロジックエレメント数が1万個以下)のFPGA、ミックスドシグナルICが、当社の製品の3本柱となっている。中でも、ミックスドシグナルICは成長している分野で、総売上高の6%を占めるようになっている」と語る。

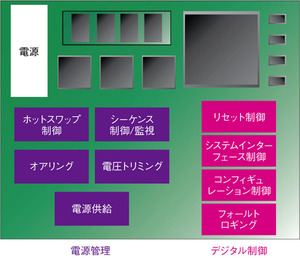

Platform Managerには、電源管理を担うブロックと、システムのデジタル制御を担うブロックの2つがある。デジタル制御を行うブロックは、Power Manager I/IIには搭載されていなかった。

電源管理を担う部分は、差動入力を用いたコンパレータ、マクロセル数が48個のCPLD、プログラムが可能なタイマー、10ビットのA-Dコンバータなどから構成される。ホットスワップ(活線抜挿)の制御、電圧/電流の監視、電源のシーケンス制御やオアリング(電源が2系統あった場合、片方に不具合が起きたときに他方に切り替えること)、電圧のトリミングといった機能を搭載している。

一方、デジタル制御を担うブロックは、プログラムが可能なデジタルI/Oと、LUT(ルックアップテーブル)数が640個のFPGAから成る。このブロックでは、リセット信号の送信、マイコンやFPGA、ASICなどに対するコンフィギュレーションのスタートアップ、ウォッチドッグタイマー、システムインターフェース制御、フォールトロギング(不具合が起きた際、その内容と時間を記録しておく機能)を行う(図1)。

通常、こうした電源管理やデジタル制御は、各機能ごとに専用のICや個別部品を用いて実現される。そのため、使用する部品点数が多くなりボード面積が大きくなる、あるいは仕様に変更を加える場合はボードの再設計が必要になるといった課題があった。

Platform Managerを利用すれば、電源管理とデジタル制御を1チップで実現することが可能になる。例えば、最大12個の電源を、0.7%の検出精度で監視することができる。0.7%の検出精度というのは、10Vの電源を監視する場合、電圧が9.93V〜10.07Vの範囲外になったら異常と見なすことができるという意味である。また、過電圧や過電流、瞬間的な電圧低下といった、電源やボード上で起こり得る問題にも、65μs以下の時間で反応する。さらに、JTAGを介して再プログラムも行える。電源管理やデジタル制御に用いる複数のIC/個別部品をPlatform Managerに置き換えることで、コストを半減できるとしている。

Platform Managerには、「LPTM10-1247」と「LPTM10-12107」の2品種がある。どちらも最大12系統の電源を監視できるが、LPTM10-1247は47本のデジタルI/Oを、LPTM10-12107は107本のデジタルI/Oを備えている点が異なる。パッケージは、LPTM10-1247が128端子TQFP、LPTM10-12107は208端子FTBGA。

参考単価は、LPTM10-1247が1000個購入時で9.00米ドル、25万個購入時で3.75米ドル。LPTM10-12107は、1000個購入時で11.50米ドル、25万個購入時で5.20米ドルとなっている。ラティスセミコンダクターは、Platform Managerの価格について、「9米ドルというのは決して安くはない。確かに2〜3系統の電源制御であれば個別部品で構成したものでも十分だが、電源の数が多い複雑なシステムほど、コストや精度といった面でPlatform Managerのメリットが生きてくる」と説明している。

Platform Manager用のソフトウエア開発ツールとしては、「PAC-Designer 6.0」と「ispLEVER Starter 8.1 SP1(以下、ispLEVER)」を用意した。PAC-Designer 6.0は電源管理(アナログ)の部分、ispLEVERはデジタル制御の部分の設計に用いる。このバージョン6.0では、前のバージョンである「PAC-Designer 5.3」とは異なり、ispLEVERから出力されたJEDECファイルを取り込むことが可能になった。また、PAC-Designer 6.0とispLEVERから出力したJEDECファイルを論理シミュレータに取り込むことで、ボードに実装する前に設計の問題点を把握できるようになる。そのため、ボードの再設計を行わなければならなくなるリスクを低減できるという。

(村尾 麻悠子)

Copyright © ITmedia, Inc. All Rights Reserved.