PSoCで構成するディレイパターン生成器:Design Ideas

デジタル回路、アナログ回路を問わず、実験などの目的でディレイパターンが必要となるケースは多い。このような状況に対応可能なものとして、筆者は1個のICでディレイパターン生成器を構成する方法を考案した。

デジタル回路、アナログ回路を問わず、実験などの目的でディレイパターンが必要となるケースは多い。このような状況に対応可能なものとして、筆者は1個のICでディレイパターン生成器を構成する方法を考案した。使用するのは、プログラマブルなアナログブロックとデジタルブロックを備えることを特徴とする米Cypress Semiconductor社の「PSoC(Programmable System on Chip)」である。以下では、PSoCファミリの「CY8C29466」を用いることを前提として話を進める。

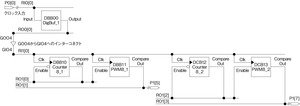

筆者が検討したディレイパターン生成器は、複数チャンネルのPWM(パルス幅変調)出力を備え、各PWM信号間のディレイ(位相差)を8ビット分解能の範囲で任意に変更可能にするというものだ。ここでは、2チャンネルの場合を例にとる。その構成は図1のようなものとなる。この回路では、ディレイを付加したPWM信号を生成するために、チャンネルごとに2つのデジタルブロックを用いている。これらのデジタルブロックとしては、開発ツール「PSoC Designer」に用意されているユーザーモジュールのうち2種類を配置する。1つは8ビット分解能のPWM信号を生成するPWMモジュール(図のPWM8_1、PWM8_2)、もう1つは8ビットのカウンタ機能を実現するCounterモジュール(図のCounter8_1、Counter8_2)である。Counterはディレイの設定用として機能させる。

また、Counter、PWMの両モジュールのほかに、デジタルバッファモジュールのDigBuf(図のDigBuf_1)も利用する。このDigBufはクロックの入力バッファとして働く。また同モジュールは、各Counter/PWMモジュールへのクロックの停止と再開の制御も担う。

次に、チャンネルごとのユーザーモジュール同士の結線について説明する。まず、Counterは「InvertEnable=Invert」に設定し、PWMは「InvertEnable=Normal」に設定しておく(イネーブル信号の正/負論理を図のように設定する)。そして、CounterのEnable入力に、自身のCompareOut出力を接続する。また、PWMのEnable入力に、CounterのCompareOut出力を接続する。さらに、Counter、PWMいずれも「CompareType=Less than Or Equal」に設定する。

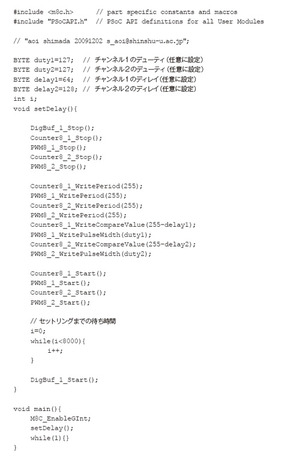

PWM信号に付加するディレイの設定プロセスをリスト1に示した。まず最初に、DigBuf、Counter、PWMをすべて停止(Stop)する。そして、Counterについては、Counter8_1、Counter8_2の周期を255に設定し(WritePeriod)、各チャンネルに必要なディレイをセットする(WriteCompareValue)。このとき、ディレイは内部的には「CompareValue」の値としてセットされる。一方、PWMについては、PWM8_1、PWM8_2に各チャンネルの周期(WritePeriod)とデューティ(WritePulseWidth)をセットする。CounterとPWMのカウント値は、周期に255という値をセットする際にリセットされるようになっている*1)。ここまでの設定を行ったら、CounterおよびPWMを起動(Start)する。

以上のようなプロセスを経た上でDigBuf_1を起動する(Start)と、各Counter、各PWMに対してクロックが入力される。そして、CounterがCompareValueの値までカウントすると、CounterのCompareOut出力がハイになる。ここでCounterのEnable入力には、自身のCompareOut出力が接続されているため、この信号がハイになることでCounterは停止し、出力がラッチされる。同時に、PWMのEnable入力にもハイが入力されるので、PWMの動作が開始する。このようにして、任意のディレイが付加されたPWM信号が生成される。

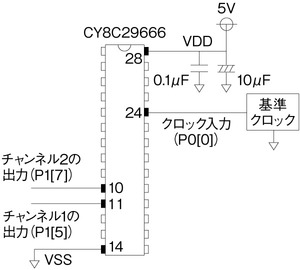

PWM信号の周期は、外部の基準クロックの周波数fCLKによって変更可能である。PWM信号の周波数fPWMはfCLK/256となるので、1MHzの基準クロックを使用した場合であれば、周波数が約3.9kHzのPWM信号が得られる。入力可能な基準クロック周波数の最大値は、PSoCのデジタル入力とデジタルブロックそれぞれのAC特性によって決まる。

CY8C29466の外部端子と周辺部品の接続は、図2のようになる。本稿では2チャンネルの場合の構成を例として示したが、これを拡張することで、より多チャンネルでフレキシブルなディレイパターン生成器を1チップで構成することが可能である。

脚注

※1…PSoC TRM, Document No. 001-14463 Rev. *E, 17.2.1.2 Counter Register Definitions, p.342

Copyright © ITmedia, Inc. All Rights Reserved.