基礎から学ぶシグナルインテグリティ:問題解決のためのポイントをつかむ(3/3 ページ)

大容量のフラッシュメモリーを搭載する機器では、従来よりも高いデータ転送速度が求められるようになっている。転送速度を高めつつ、転送時のエラーを低減するには、シグナルインテグリティの対策が重要となる。本稿では、高速デジタル信号を扱う機器を設計する際に、シグナルインテグリティを確保するために必要となる基礎知識や設計手法について説明する。

プリント基板での対策

信号変化の多い回路や、ICのパッケージ、コネクタはすべてシグナルインテグリティに影響を与える。また、プリント基板もシグナルインテグリティに影響を与えるが、多くの場合、その影響の度合いを見極めるのは難しい。データ転送速度の高速化や機器の低コスト化が進む中で、その要求にプリント基板が対応できないことも多い。例えば、低コストのプリント基板材料として知られるFR4(ガラスエポキシ基板)は、データ転送速度が比較的低い用途には利用できるものの、10ギガビット/秒を超えるような高速のデータ転送速度の用途には適していない。

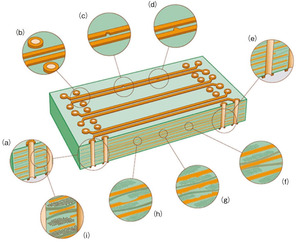

図5に、プリント基板の構造において、シグナルインテグリティに影響を及ぼす可能性がある部分を示した。まず、貫通電極に過剰な静電容量が存在すると、差動伝送路の特性に影響が及ぶ可能性がある(図5(a))。これについては、使用するアンチパッド(開口部)を大きくすることで対処できる。また、差動伝送路に近接するビア間では、局所的なクロストークが発生することがある(図5(b))。この問題は、配線の間隔を広げることによって解決できる。図5(c)のように、導体幅が一様でないことによる影響は、配線幅を太くすることによって対処できる。図5(d)のように、配線の間隔が均一でない場合は、配線間隔を広げることで対処する。

ビアのスタブ(配線分岐)は容量性の反射を引き起こし、伝送路のインピーダンスに負荷をかける可能性がある(図5(e))。このような問題に対しては、代わりにブラインドビアや埋め込みビア、バックドリルビアの使用を検討する必要がある。プリント基板の誘電性が一様でない場合には、ローフロー材料や合成繊維製のプリプレグを試してみてもよいだろう(図5(f))。

表面処理によって厚みのむらが生じることがある(図5(g))。こうしたむらは、めっきや上塗りなどの仕上げ処理によって対処できる。金属箔の厚みを部分的に変更するには、プリント基板の材料や製造プロセスを調整する(図5(h))。エポキシ樹脂とガラス繊維の薄い層の中に存在するすき間は、CAF(Conductive Anodic Filament)によるショートを引き起こす可能性がある(図5(i))。この問題に対処するには、絶縁層を追加するか、層を厚くする必要がある。

次世代のフラッシュメモリーを搭載する機器において、実際に“次世代”のレベルのデータ転送速度を実現するには、シグナルインテグリティに対する意識を高めることが必要になる。シグナルインテグリティに影響を与える可能性がある要因と、そのモデル化および物理的測定の手法を理解していれば、高い信頼性と優れた性能を備えた製品を、予算の範囲内かつ納期どおりに設計することができるだろう。

Copyright © ITmedia, Inc. All Rights Reserved.