回路シミュレータの最新動向を探る(後編):SoCの不具合を見逃さないために(1/2 ページ)

デジタル回路とアナログ回路を混載する大規模なSoCの設計には、回路シミュレータをはじめとするEDAツールが必要不可欠である。本稿の後編では、回路シミュレータとテストベンチの統合、ハードウエアベースの回路エミュレータ、アナログ回路とデジタル回路の協調シミュレーションに関する、EDAツールベンダーの最新の取り組みを紹介する。

テストベンチとの統合

Cadence Design Systemsで検証プロダクト担当のマーケティングマネジャーを務めるTom Anderson氏は、「エンジンの性能を上げただけでは検証プロセスに関する問題を解決することはできない」と語る。回路が複雑化したことにより、検証プロセスは低消費電力、RTLシミュレーション、デジタル回路とアナログ回路を混載するミックスドシグナル、フォーマル解析などのより細かいプロセスに分かれた。同社で検証プロダクト担当のマネジメントディレクターを務めるAdam Sherer氏も、「シミュレーション性能は重要だが、それだけでは十分ではない」と繰り返す。同氏は、「回路規模の大きなSoC(System on Chip)では、エラボレーション(シミュレーション条件の無矛盾性を確認すること)プロセスの回数が増える。そのため、エラボレーションの高速化と差分処理の両方が必要になる」と述べる。さらに、「ユーザーは、波形やカバレッジデータベースに対するアクセスの高速化とともに、データベース容量の圧縮も要求している」と続けた。

Cadenceの検証ツール「Incisive」の最新版であるバージョン10.2では、設計や電力に関する意図を1つの検証プランに関連付けることができるほか、メトリクスドリブン検証(MDV)による制御で、デジタル回路やミックスドシグナル回路を抽象化した定型モデルを結合することもできる。検証技術者はMDVを使用して、シミュレーションの結果を用いてフォーマル解析したカバレッジのデータを、単一化されたSoCレベルの検証プランに統合できる。MDVの中でフォーマル解析と動的解析を結びつけることによって、フォーマル検証ツールを使用して回路内の到達できていない点に印をつけ、シミュレーションをする必要がないことを示すことができる。Incisiveも、シミュレーションやフォーマル解析のためのアサーションおよびカバレッジポイントを自動的に生成できることから、検証プランの各部分を実行するためにどのシミュレータを使用すればよいかを定義しやすくなる。

Incisiveでは、リアルナンバーモデル(実数モデル)がデジタル動作とミックスドシグナル動作のインタフェースの役割を担っている。Cadenceは、Incisive 10.2において、UVM向けにシミュレータの性能を最適化した。Incisiveは、シミュレーションの中でUVMコンポーネントをネイティブオブジェクトとして取り込み、その動きを波形表示器で表示/計測できる。また、検証言語のe言語に対応できるようにOVMとUVMを拡張し、テストベンチで複数の言語が使用できるようにした。ほかにも、Verilog、VHDL(Very High Speed Integrated Circuit Hardware Description Language)、PSL(Property-Specification Language)、e、SystemC、System Verilog(SV)など、IEEEが策定した検証言語のすべてをサポートしている。何度も行われるリグレッションテスト(回帰テスト)における性能を向上するためのIncisiveのオプション機能として知られているのが「Specman」である。Specmanによって、e言語ベースでのテストの再シードや動的ローディング、複数のプロセッサコアによるe言語のコンパイル、インタープリットおよびコンパイルされたコードを混在させることによってデバッグ時間を短縮する機能などが提供される。

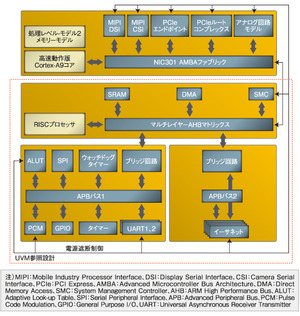

また、Incisiveのユーザーは、Incisiveの検証キットを利用することができる。同キットを用いることで、ゲート数が150万個のイーサネットコントローラ向けSoCの回路に関する機能検証のデモンストレーショを行うことができる。機能検証のコンセプトを学ぶための教材としてはうってつけといえよう(図2)。

存在感増す回路エミュレータ

Eve USAでゼネラルマネジャーを務めるLauro Rizzatti氏は、ハードウエアベースの回路エミュレータが勢力を取り戻していることを示すEDAコンソーシアム(EDAC)の調査データを提示した。同氏によると、「ソフトウエアベースのシミュレーションでは、開発期間の間にSoCの回路全体の検証を完了したり、その検証結果を組み込みソフトウエアの開発にまで用いたりするようなスピードは期待できない」という。

EDAツールのうち、シミュレーション関連ツールの市場規模は、2007年に過去最高となる5億3200万米ドルを記録した後、2010年には3億2300万米ドルまで減少している。その一方で、回路エミュレータの市場規模は、1億4000万米ドル〜1億6000万米ドルの範囲でほとんど変化がない。つまり、ソフトウエアベースのシミュレーションツールと、ハードウエアベースの回路エミュレータを合わせた、検証ツール市場全体に対する回路エミュレータの割合は増加していることになる。Rizzatti氏は、「10年前、回路エミュレータはCPUベンダーやGPU(Graphics Processing Unit)ベンダーだけにとって重要なツールだった。しかし、現在は、無線通信、マルチメディア、ネットワーク、イメージプロセッシングなどの各機器市場向けのICの設計用途にも利用される事例が増えている」と指摘する。現行の回路エミュレータは、業界標準のVerilogやSV、VHDLベースのソフトウエアシミュレータに対応するテストベンチと連携して動作する。このとき、シミュレーションの実行速度は、1秒当たり数百万サイクルに達する。

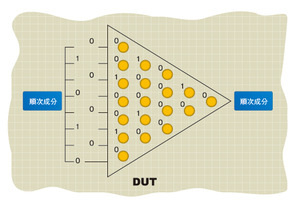

かつて、回路エミュレータは大変高価だったために、利用される機会は限定されていた。この高価であるため利用できないという問題に対して、Eve USAは、回路エミュレータに用いるメインのICについて、ASICに替えてXilinxのハイエンドFPGA「Virtexシリーズ」を使用することによって低価格化を進めている。FPGAを用いた回路エミュレータは、シミュレーションの実行速度は速いものの、出力結果の可視性が低いというデメリットがある。現在、Eve USAは、同社の回路エミュレータ「ZeBu(Zero Bug)」プラットフォームに、CSA(Combinational Signal Access)と呼ぶ機能を追加することによってデバッグ機能を拡張している。CSAによって動的プローブの使用が可能になるので、回路内のレジスタやメモリー間の円錐状の論理回路内にあるRTL(レジスタトランスファレベル)のネットリストをすべて確認できるようになるのである(図3)。CSAの処理結果は、標準的なVCDまたはFSDB形式のファイルで出力することができる。さらに、パソコンやLinuxワークステーション上でエミュレーションを実行したあとに生成した波形とCSAを利用することにより、オフライン解析を行うことも可能である。

Mentor GraphicsのBailey氏も、回路エミュレータの存在感が増していることを認めている。特に、テストシーケンスが長すぎるためにソフトウエアベースのシミュレーションだけで対応するのに時間がかかりすぎるマルチメディア機器向けICの設計では、回路エミュレータは必須といえよう。Mentorの検証プラットフォーム「Veloce」は、カスタムチップによるアクセラレーション処理を適用することにより大規模なSoCのエミュレーションが可能であるとともに、ソフトウエア/ハードウエア協調検証を行えることも特徴となっている。Veloceでは、設計したSoCのモデルを対象となる実機の検証環境に接続して、被試験回路(DUT: Device Under Test)を動作させる実データを用いた組み込みソフトウエアを実行することにより、インサーキットエミュレータとしても使用できる。

Copyright © ITmedia, Inc. All Rights Reserved.