デジタル制御電源を学ぶ(4) 複雑な電源は機能分析から制御方式を見極める:Design Hands-on(2/3 ページ)

実践編の2回目となる本稿では、ブーストコンバータを用いた2相インターリーブPFCを取り上げ、デジタル制御の実装過程を解説していく。複数の機能を備えるこの複雑な電源回路でも、実装の手順そのものは前回のバックコンバータと変わらない。機能ごとに要件を分析していけば、どのように制御すべきかが見えてくる。

I/Oレジスタの設定方法を確認する

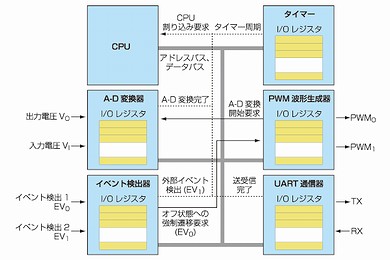

デジタル制御ICを構成する各ハードウェアブロック(タイマー、A-D変換器、PWM波形生成器、イベント検出器、UART通信器)の処理内容が決定したら、I/Oレジスタの設定でどのように各ハードウェアを動作させるか見ていこう。前回のバックコンバータとの違いは、タイマーからのCPU割り込み要求とPWM波形生成器からの出力が追加された点である(図2)。

まずは電圧制御だ。PWM波形生成器は、スイッチング周期でPWM0とPWM1から180度の位相差を持つ2つの矩形波を出力するとともに、A-D変換器に対して変換開始の要求を出す。A-D変換器はこれを受けて処理を始め、入力電圧と出力電圧の大きさをA-D変換してデジタルデータ化し、それが完了するとCPUに割り込み要求を発行する。また、タイマーは、100μsのタイマー周期でCPU割り込み要求を出す。これらの動作はそれぞれスイッチング周期とタイマー周期で繰り返すので、CPUへの割り込み要求は固定周期で生じることになる。

次は、過電圧保護とUART通信だ。過電圧保護では、外部イベント入力(EV1)を監視しているイベント検出器が外部イベントの発生を捉えたときに、そしてUART通信ではUART通信器の送受信が完了したときに、それぞれCPU割り込み要求を出す。これらの動作は過電圧やUART通信が発生した場合しか実行されないので、CPU割り込み要求は不定期に生じる。

そして、電圧制御の周期処理、過電圧保護とUART通信の即時処理いずれもCPUに割り込みを要求しているため、あらかじめそれぞれのCPU割り込み要求にソフトウェア処理を関連付けておけば、CPU割り込み要求が発生するたびにその処理が実行される。

最後は過電流保護だ。イベント検出器はEV0入力の外部イベントを検出すると、PWM出力をオフ状態へ強制的に遷移させる要求を出す。PWM波形生成器はこれを受けてPWM信号の出力(PWM0とPWM1)をその周期内のみオフ状態に遷移させる。この動作は、CPUが介在せずにハードウェアブロック同士が連動するので、処理時間に100ns以内という制約がある処理に適用できる。

ソフトウェアの基本構成を準備する

I/Oレジスタの設定が確認できたら、ソフトウェアの基本構成を準備しよう。(a)通常処理、(b)周期処理、(c)即時処理の3つに分類した各処理ごとに、関数と呼ばれるソフトウェアのまとまりを準備する作業だ。今回取り上げている電源では、周期処理として電圧制御のPI制御フィルタとAC電流波形補正の2つ、即時処理として過電圧保護とUART通信の2つをCPU割り込み関数として準備すればよい。それぞれのソフトウェア処理の流れは、固有のものではなく、任意のデジタル制御に適用できるものなので、前回のバックコンバータを参照してほしい。

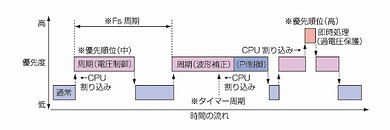

図3は、実行優先順位に基づくソフトウェア処理の流れを時系列で示したものだ。CPUは、優先順位の高い割り込みが発生すると、現在の処理を保留して優先順位の高い処理を先に終了させる。ここでは、電圧制御のPIフィルタ処理とAC電流の波形補正処理を合わせた処理時間をスイッチング周期内に収めることが重要である。その理由はこうだ。タイマー周期のCPU割り込み要求の発生頻度はスイッチング周期の1/8だが、両者は同じ優先順位にあるので、あるスイッチング周期では両者を合わせた処理時間が必要となり、もし収まらなければ時比率が更新されない周期が生じてしまうからである。

Copyright © ITmedia, Inc. All Rights Reserved.