•،ژG‚بA/DƒRƒ“ƒoپ[ƒ^‚ج‰ٌکHچ\گ¬‚ً‹ة‚ك‚éپIپF‚¢‚ـ‚³‚ç•·‚¯‚ب‚¢ƒRƒ“ƒoپ[ƒ^“ü–هپi2پjپi1/3 ƒyپ[ƒWپj

–¯گ¶‹@ٹيپAŒv‘ھپA’تگMپAژ©“®ژشپAچH‹ئ‹@ٹيپAˆم—أٹي‚ب‚اپA‚³‚ـ‚´‚ـ‚ب•ھ–ى‚ةژg‚ي‚ê‚ؤپuƒfپ[ƒ^پEƒRƒ“ƒoپ[ƒ^پvپBچ،‰ٌ‚حA/DƒRƒ“ƒoپ[ƒ^‚ة‚آ‚¢‚ؤ‰ًگà‚·‚éپB

پ@‘O‰ٌ‚حƒپƒWƒƒپ[‚بƒRƒ“ƒoپ[ƒ^‘fژq‰ٌکH‚ج“ء’·پA‚»‚µ‚ؤ‚»‚جژg‚¢•û‚جٹî–{‚ئ‚µ‚ؤپAD/AƒRƒ“ƒoپ[ƒ^‚ًڈذ‰î‚µ‚ـ‚µ‚½پBچ،‰ٌ‚حA/DƒRƒ“ƒoپ[ƒ^‚ة‚آ‚¢‚ؤ‰ًگà‚µ‚ـ‚·پB

A/DƒRƒ“ƒoپ[ƒ^‚جٹî–{چ\گ¬‚ئ‚»‚ج“ء’·

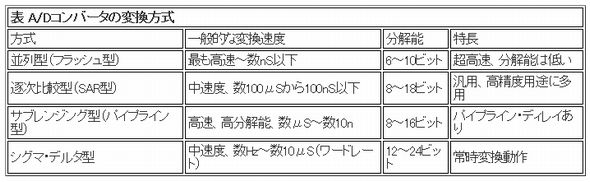

پ@ƒAƒiƒچƒO“ü—حگMچ†‚ًƒfƒWƒ^ƒ‹ڈo—حگMچ†‚ة•دٹ·‚·‚éA/DƒRƒ“ƒoپ[ƒ^‚ة‚حپAD/AƒRƒ“ƒoپ[ƒ^‚و‚è‚à‘½‚‚ج‰ٌکHچ\گ¬‚ھ‚ ‚è‚ـ‚·پBŒ»چفچL‚ژg‚ي‚ê‚ؤ‚¢‚é•ûژ®‚حپAˆب‰؛‚ج•\‚ة‚ ‚é‚à‚ج‚إ‚·پB

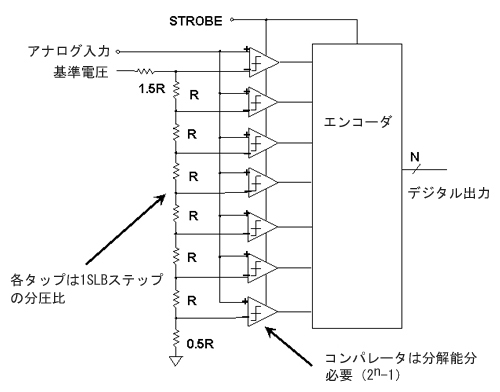

پ@‘O‰ٌپA‘½‚‚جA/DƒRƒ“ƒoپ[ƒ^‚حپA“à•”‚ة”نٹr—p‚جD/AƒRƒ“ƒoپ[ƒ^‚ً“à‘ ‚µ‚ؤ‚¢‚é‚ئڈq‚ׂـ‚µ‚½‚ھپAƒtƒ‰ƒbƒVƒ…پEƒRƒ“ƒoپ[ƒ^‚ئŒؤ‚خ‚ê‚é•ہ—ٌŒ^A/DƒRƒ“ƒoپ[ƒ^‚حپA‚»‚±‚ةƒfƒWƒ^ƒ‹ƒ|ƒeƒ“ƒVƒ‡ƒپپ[ƒ^Œ^‚ج‘fژq‚ًژg—p‚µ‚ؤ‚¢‚ـ‚·پB‚±‚ج’ïچR‚جƒ^ƒbƒv‚ج“dˆ³‚ئ“ü—ح‚³‚ꂽƒAƒiƒچƒOگMچ†‚ج“dˆ³‚ًپAچ‚‘¬ƒAƒiƒچƒOپEƒRƒ“ƒpƒŒپ[ƒ^‚إ”نٹr‚µپA‚»‚جˆت’u‚ًƒfƒRپ[ƒh‚µ‚ؤƒfƒWƒ^ƒ‹’l‚ة•دٹ·‚µ‚ـ‚·پB

پ@ڈ]‚ء‚ؤپA•دٹ·‘¬“x‚حپA‚ظ‚ئ‚ٌ‚ا‚±‚جƒRƒ“ƒpƒŒپ[ƒ^‚ج”½‰‘¬“x‚ة‚و‚茈‚ـ‚è‚ـ‚·پBA/DƒRƒ“ƒoپ[ƒ^‚جچ\گ¬‚ئ‚µ‚ؤ‚حپAچإ‚àچ‚‘¬‚ج“®چى‚ھٹْ‘ز‚إ‚«‚éپi’ل‚¢•ھ‰ً”\‚إ‚حGHz‘رˆو‚ج•دٹ·‚ھ‰آ”\پj‚ج‚إپAƒfƒWƒ^ƒ‹پEƒXƒgƒŒپ[ƒWپEƒXƒRپ[ƒv‚ب‚ا‚ةژg—p‚³‚ê‚ؤ‚¢‚ـ‚·‚ھپAچإ‹ك‚إ‚حŒم‚ةڈq‚ׂéƒTƒuƒŒƒ“ƒWƒ“ƒOŒ^‚âƒVƒOƒ}پEƒfƒ‹ƒ^Œ^A/DƒRƒ“ƒoپ[ƒ^“à•”‚جƒrƒ‹ƒfƒBƒ“ƒOپEƒuƒچƒbƒN‚ئ‚µ‚ؤژg‚ي‚ê‚邱‚ئ‚ج•û‚ھ‘½‚¢‚و‚¤‚إ‚·پB

پ@‚±‚ج•ûژ®‚جژم“_‚حپA•ھ‰ً”\‚جگ”‚¾‚¯ƒRƒ“ƒpƒŒپ[ƒ^‚ھ•K—v‚إپA‚»‚ج‹K–ح‚ھ”ٌڈي‚ة‘ه‚«‚‚ب‚ء‚ؤ‚µ‚ـ‚¤‚±‚ئ‚إ‚·پB—ل‚¦‚خ10ƒrƒbƒg‚جڈêچ‡پA1024Œآ‚جƒRƒ“ƒpƒŒپ[ƒ^‚ھ•ہ—ٌ‚ةگع‘±‚³‚êپA“ü—حگMچ†‚ح‚±‚ê‚ç‚ً’ل‚ن‚ھ‚ف‚إ‹ى“®‚·‚邽‚ك‚ةپA‚»‚ج‹ى“®ƒAƒ“ƒv‚ة‚©‚ب‚è‹—ح‚ب‚à‚ج‚ً•K—v‚ئ‚µ‚ـ‚·پB‚ـ‚½’ïچRƒXƒgƒٹƒ“ƒO‚جگ¸“x‚âپAƒRƒ“ƒpƒŒپ[ƒ^‚جگ¸“x‚ة‚و‚éƒٹƒjƒAƒٹƒeƒBƒGƒ‰پ[‚ھ‚ ‚邽‚كپA‚¢‚ـ‚ج‚ئ‚±‚ë10ƒrƒbƒg’ِ“x‚ھ‚»‚جŒہٹE‚إ‚·پB

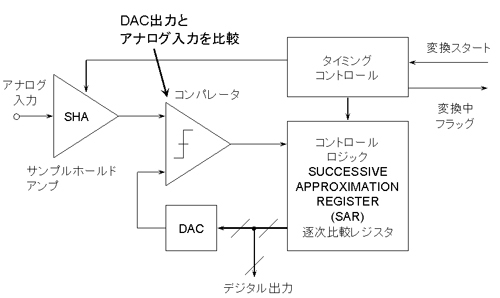

پ@•ہ—ٌŒ^‚ح”نٹr‚ًˆê•ص‚ةچs‚¢‚ـ‚µ‚½‚ھپA‚±‚ê‚ًD/AƒRƒ“ƒoپ[ƒ^‚ج1ƒrƒbƒg‚²‚ئ‚ةƒVƒٹƒAƒ‹‚ةچs‚¤‚و‚¤‚ة‚µ‚½‚à‚ج‚ھپA’€ژں”نٹrŒ^پiSuccessive Approximation Registerپ@—ھ‚µ‚ؤSARپjA/DƒRƒ“ƒoپ[ƒ^‚إ‚·پiگ}2‚ًژQڈئ‚µ‚ؤ‚‚¾‚³‚¢پjپB

پ@”نٹr‚حSAR‚ئ‚¢‚¤ƒVپ[ƒPƒ“ƒT‚ة‚و‚èƒVƒٹƒAƒ‹‚ةچs‚ي‚ê‚邽‚كپAƒRƒ“ƒpƒŒپ[ƒ^‚ح1‚آ‚إچد‚ف‚ـ‚·پB”نٹr‚ح“à‘ D/AƒRƒ“ƒoپ[ƒ^‚جƒrƒbƒgگ”‚¾‚¯چs‚ي‚ê‚ـ‚·پB•دٹ·‚جƒAƒ‹ƒSƒٹƒYƒ€‚ح15گ¢‹I‚©‚ç’m‚ç‚ê‚ؤ‚¢‚é•û–@‚إپA‚ؤ‚ٌ‚ر‚ٌ‚إ–¢’m‚جڈd‚³‚ًچإڈ¬‚جŒv‘ھ‰ٌگ”‚إ—ت‚é•û–@‚ً‰—p‚µ‚½‚à‚ج‚إ‚·پB

پ@گ}2‚ً‚²——‚‚¾‚³‚¢پB1پA2پA4پA8پcپc‚ئ‚¢‚¤ڈd‚ف‚ًژ‚ء‚½D/AƒRƒ“ƒoپ[ƒ^‚جٹeƒrƒbƒgڈo—ح‚ئ“ü—حگMچ†‚ً”نٹr‚µ‚ؤپAٹeƒrƒbƒg‚جƒIƒ“پEƒIƒt‚ًŒˆ‚ك‚ؤ‚¢‚«‚ـ‚·پBچإڈI“I‚ة‚حD/AƒRƒ“ƒoپ[ƒ^‚جƒRپ[ƒh‚ھپA•دٹ·ƒfپ[ƒ^‚ئ‚ب‚è‚ـ‚·پB

پ@‚±‚جD/AƒRƒ“ƒoپ[ƒ^•”•ھ‚حپAچإ‹ك‚إ‚ح’ïچRƒ‰ƒ_پ[‚إ‚ح‚ب‚ƒRƒ“ƒfƒ“ƒT¥ƒ‰ƒ_پ[‚ة‚و‚é‚à‚ج‚ھ‘‚¦‚ؤ‚«‚ؤ‚¢‚ـ‚·پB‚±‚جƒRƒ“ƒoپ[ƒ^‚حپAƒrƒbƒg‚ًڈ‡”ش‚ة”نٹr‚µ‚ؤ‚¢‚‚½‚كپA‚»‚جƒVپ[ƒPƒ“ƒX‚جچإ’†‚ة“ü—حگMچ†‚ھ1LSBˆبڈم“®‚¢‚ؤ‚µ‚ـ‚¤‚ئپiD/C‚â‹ة’لژü”g‚إ‚ح–â‘è‚ب‚¢پjپA‚»‚جŒ‹‰ت‚ھ•sگ³ٹm‚ة‚ب‚è‚ـ‚·پB

پ@‚»‚ج‚½‚كپA“ü—حگMچ†‚ج“®‚«‚ً•دٹ·’†‚¾‚¯ˆêژژ~‚ك‚éپAƒTƒ“ƒvƒ‹پEƒzپ[ƒ‹ƒhپEƒAƒ“ƒv‚ ‚é‚¢‚حƒgƒ‰ƒbƒNپEƒzپ[ƒ‹ƒhپEƒAƒ“ƒv‚ھ‚ظ‚ئ‚ٌ‚ا‚جڈêچ‡•K—v‚إ‚·پBچإگV‚جƒfƒoƒCƒX‚حپA‚±‚ج‰ٌکH‚ًƒ`ƒbƒvڈم‚ةڈWگد‚µ‚ؤ‚¢‚ؤپAƒTƒ“ƒvƒٹƒ“ƒOA/DƒRƒ“ƒoپ[ƒ^‚ئŒؤ‚خ‚ê‚邱‚ئ‚à‚ ‚è‚ـ‚·پB

پ@’€ژں”نٹrŒ^A/DƒRƒ“ƒoپ[ƒ^‚حپAˆµ‚¢‚â‚·‚¢‰ٌکH‹K–ح‚ئ”نٹr“I’لƒmƒCƒY‚إپAŒ»چف”ؤ—p‚©‚çچ‚گ¸“xƒRƒ“ƒoپ[ƒ^‚ج•ھ–ى‚إچإ‚àچL‚ژg‚ي‚ê‚ؤ‚¢‚ـ‚·پB8ƒrƒbƒg‚©‚ç18ƒrƒbƒg‚ئ‚¢‚¤چ‚گ¸“x‚ج‚à‚ج‚ـ‚إپAƒ‚ƒmƒٹƒVƒbƒNIC‚ئ‚µ‚ؤ‹ں‹‹‚³‚ê‚ؤ‚¢‚ـ‚·پB•دٹ·‘¬“x‚حƒrƒbƒgگ”‚ة‚à‚و‚è‚ـ‚·‚ھپAگ”10K SPSپiKilo Samples Per Secondپj‚©‚çگ”10MSPSپiMega Samples Per Secondپj‚‚ç‚¢‚ـ‚إ‚إ‚·پB

Copyright © ITmedia, Inc. All Rights Reserved.