専用プロセッサとしてのDSPの特徴:イチから学ぶDSP基礎の基礎(2)(1/3 ページ)

今回は、専用プロセッサとしてのDSPの特徴と、DSP出現の背景、DSPと汎用CPUの違いについて解説します。

前回はDSPが得意とする仕事と、アプリケーションによる処理遅延の重要性についてお話しました。

今回は、専用プロセッサとしてのDSPの特徴と、DSP出現の背景、DSPと汎用CPUの違いについてお話します。

専用プロセッサとしての特徴

専用プロセッサとしてのDSPの特徴は、次の6点です。

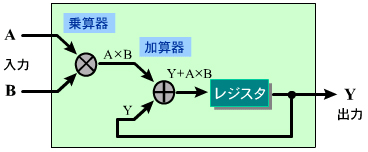

(1) 1クロックで積和演算を行うための積和演算器(乗算器+加算器)を備えている

(2) 2系統の分離独立したメモリとバスを備えている(ハーバード・アーキテクチャと呼ばれる構成)

(3) ループ制御のための専用命令を備えている

(4) 大容量のメモリを内蔵している

(5) 大量のデータを入出力できるように強力なI/O(入出力回路)を備えている

(6) FFT専用のビット逆順アドレッシング回路等を備えている

以下、順を追って説明します。

(1) 1クロックで積和演算を行うための積和演算器(乗算器+加算器)を備えている

デジタル信号処理(離散時間信号処理)は、積和演算(乗算と加算の組み合わせ)の形の処理が多いです。下の式は、連続的にNクロック動作させた式で、これを見ると積和演算の繰り返しとなっています。

そこでDSPでは、この積和演算を高速で実行させるために、積和演算器(乗算器+加算器)を搭載しています。

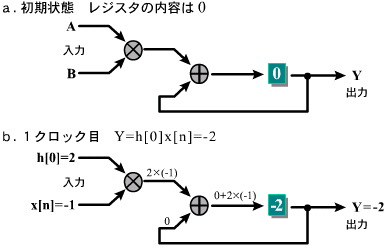

デジタル信号処理の演算の中で最も基本的なFIRフィルタを調べてみると、実はFIRフィルタは積和演算の形になっているのです。

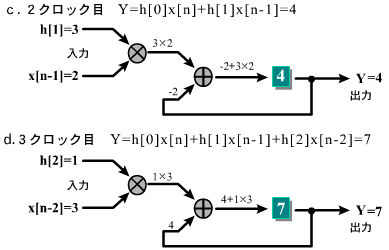

先ほどの繰り返し積和演算の式とは変数の引数の順番が異なっていますが、FIRフィルタも積和演算の形をしているDSPの積和演算器を使えば、NタップのFIRフィルタの演算はNクロックで実行できます。

NタップFIRフィルタの演算式で、h[0]=2、h[1]=3、h[2]=1、x[n]=-1、x[n-1]=2、x[n-2]=3とすると、3タップFIRフィルタの積和演算は、下の式となります。

図2は積和演算器の初期状態と、1クロック目の処理です。

図3は積和演算器の2クロック目、3クロック目の処理です。

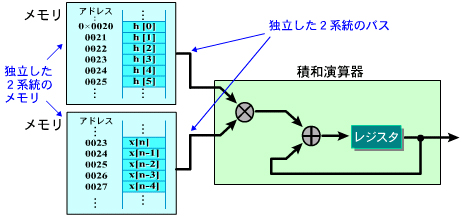

(2) 2系統の分離独立したメモリとバスを備える

積和演算器を使って1クロックで積和演算を行うためには、1クロックで積和演算器の入力に2つのデータを供給する必要があります。

図4はDSPでの積和演算に注目したハーバード・アーキテクチャの説明図です。プロセッサ・アーキテクチャの解説書などでは、ハーバード・アーキテクチャはプログラム・メモリとデータ・メモリが独立、それぞれのバスも分離しているのが特徴として説明されています。

(3) ループ制御のための専用命令を備えている

連続的に高速で積和演算を行うためには、繰り返し回数の制御も高速化する必要があります(ループ回数を専用レジスタにセットしておけば、ループ制御変数のインクリメント/デクリメント・終値条件の判定は専用ハードウェアが自動的に処理してくれます)。

(4) 大容量のメモリを内蔵している

処理量の多い複雑な演算をこなします。外部メモリを読み書きするには内蔵メモリよりも余分なクロック数が掛かるので、できる限り外部メモリの使用を避けるために、大容量メモリを内蔵しています。

(5)大量のデータを入出力できるように強力なI/O(入出力回路)を備えている

DSPは単位時間内に大量のデータストリームを入力し、その処理結果を出力します。

(6)FFT専用のビット逆順アドレッシング回路等を備えている

FFT(高速フーリエ変換)には一般のプロセッサでは処理しにくい特殊な演算が含まれていますが、その演算を高速化します。

Copyright © ITmedia, Inc. All Rights Reserved.