ブラックボックスのFPGA、基板の回路設計に潜むわな:Wired, Weird(2/3 ページ)

基板の回路図ではFPGAは単なる「ボックス」状のシンボルとしてしか描かれておらず、そこから入出力の情報を読み取ることは不可能だ。しかしFPGAの内部に構築された回路を把握しなければ、入出力の条件は分からないのである。それが障壁となって、不具合のトラブルシューティングを阻んでしまう。

正常動作を妨げていたのはFPGA

そこで、フォトカプラの出力側に負荷としてつながる部品の方を確認してみた。Vceが0.2Vのフォトカプラの接続先は、ルネサス エレクトロニクス製のCPLDだった。

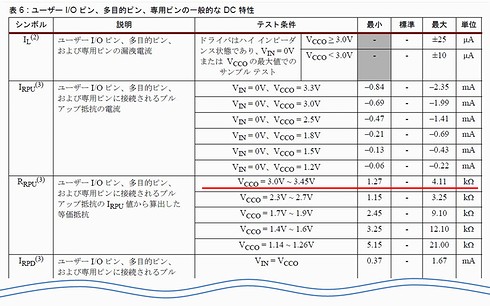

一方、Vceが2.9Vに達していたものはXilinx(ザイリンクス)製のFPGAにつながっていた。ここでCTRを保証値である100%と仮定して、電圧降下と電流から負荷抵抗の大きさを逆算すると、0.4V÷0.4mA=1kΩと求められる。すなわち、フォトカプラの出力がつながるFPGAの入力端子は、FPGAの内部で1kΩ程度の抵抗を介して電源にプルアップされている計算になる。そこでFPGAの入出力端子のDC特性をデータシートで確認した。図2がその抜粋である。

図2中、赤色の線を引いた部分に注目いただきたい。この基板におけるFPGAの電源電圧(VCCO)は3.3Vなので、ここに記述されている「プルアップ抵抗(RRPU)は1.27〜4.11kΩ程度」という仕様が適用される。先ほど実測値から求めた「1kΩ程度」に合致した。

フォトカプラに1kΩの負荷がつながった状態では、内蔵するフォトトランジスタに流れる電流(IC)は3mAになる。LEDに流れる電流(IF)が2mAでCTRが100%という条件では、フォトカプラの出力電圧が1Vを超えてしまう。これでは、FPGAが入力信号の論理レベルを「Low」と判断するしきい値として規定された「0.8V以下」を満たせない。そのため、センサーの信号を検出できなかったと考えられる。

一般にFPGAは、内部のロジック回路のみならず、入出力端子のプルアップやプルダウンの条件についてもプログラムでユーザーが設定できる。この不良基板の場合、確かに前述の計算では「1kΩのプルアップが入っている」と推定できたが、実際のところはどうなのだろうか? 冒頭で指摘した通り、こうしたFPGA内部の状態は基板の回路図には示されていない。そこで、不良基板の修理を依頼してきた顧客にこの検証結果を報告し、FPGAの入出力端子の設定について確認したところ、やはり入力端子にプルアップ抵抗が接続されていた。

地道な作業が確固たる技術への道

これは明らかに設計のミスだ。それにしてもなぜこのような設計ミスが生じ、しかも今まで見過ごされてきたのか? どうして開発時の設計検証(デザインレビュー)でつぶせなかったのか?

この問題には、設計者が基板を検証する際の意識も少なからず影響しているはずだ。「基板が動けば良い」という考えで基板全体の機能動作を確認していると、細部が全く見えなくなる。基板上の部品1つ1つの動作が設計時の想定に合致しているかどうかをテスターやオシロスコープで確かめれば、各部品の挙動を把握でき、このような“うっかりミス”は防止できる。

また回路図を作成する際に、FPGAのように内部にプルアップ回路がある部品については、回路図の中にその値をメモ書きしておくのが有効だ。今回の事例でもそうしていれば、デザインレビュー時にレビュアーの目にとまり、不良を作り込んだまま基板を世に出してしまうことは防げただろう。

これは筆者の経験だが、地道な作業を行うことで、部品の特性をよく理解できるし、部品1つ1つの特性をしっかりと把握して身につけることができる。そうすれば、確固たる技術を備えた設計者へと成長することができると思う。また、回路図を「第三者が見ても分かりやすいように書く」という習慣をつければ、関連する部門の担当者の協力やアドバイスを得やすくなる。

Copyright © ITmedia, Inc. All Rights Reserved.