外付けFETの“電子抵抗素子”でゲイン制御アンプを実現、AGCにも応用可能:オペアンプ+トランジスタ“ちょい足し”回路集(12)

オペアンプICに個別部品を“ちょい足し”して性能を高めたり機能を拡充したりできる定番回路集。約1年にわたってお届けしてきた本連載は今回が最終回です。今までおつきあいくださり、ありがとうございました。今回は、FETを“ちょい足し”してゲイン制御アンプを実現する方法を紹介します。

今回紹介する回路の概要

| 実現できる機能 | オペアンプのゲインを入力信号のレベルに応じて自動的に調整できる。 |

|---|---|

| こんな場面で有効 | 周囲の騒音に応じて放送音声を調節するなどの応用が可能。 |

今回は、オペアンプのゲインを制御する回路を紹介します。入力信号をオペアンプで増幅する際に、その入力信号のレベルに応じてオペアンプのゲインを調整する回路です。これを応用すれば、自動利得制御(AGC:Automatic Gain Control)機能も実現することもできます。例えば、周囲の騒音に応じて放送音声を調節するなどのアプリケーションが考えられます。

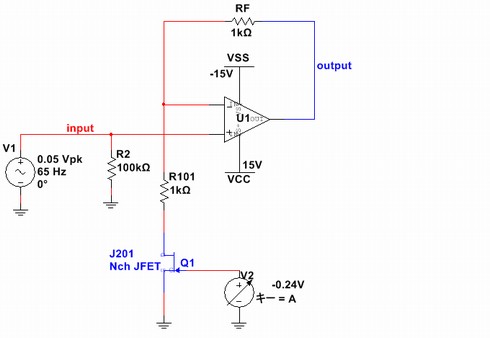

今回“ちょい足し”するのはJFET(接合型FET)です。図1をご覧ください。

オペアンプIC(U1)は非反転増幅回路の構成になっており、信号源(V1)の出力をU1への入力信号として非反転入力(+)端子に印加しています。この入力信号を、帰還抵抗(RF)とJFET(Q1)からなる回路で決まるゲインで増幅して出力します。ここで、Q1のゲート・ソース間電圧(VGS)を調整すると、ドレイン・ソース間の等価抵抗の値が変化するので、U1のゲインを可変にできる仕組みです。

Q1はnチャネル型のJFETです。今回は、このJFETをソース接地回路として、VGSを変化させることでドレイン電流(ID)を調整し、“電子抵抗素子”として機能させています。

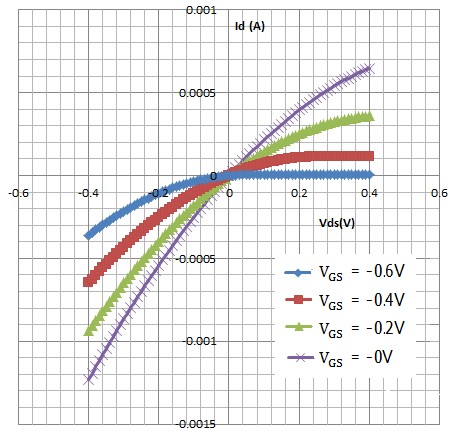

抵抗素子として動作していることを確認するために、回路シミュレータ上でJFETのVGSを−0.6V〜+0Vの範囲で変化させ、IDとドレイン・ソース間電圧(VDS)の値を求めました。その結果を図2に示します。

設計上の注意点

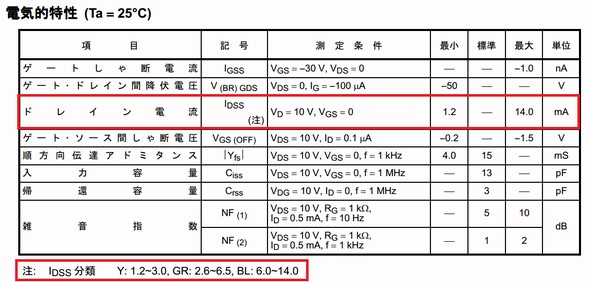

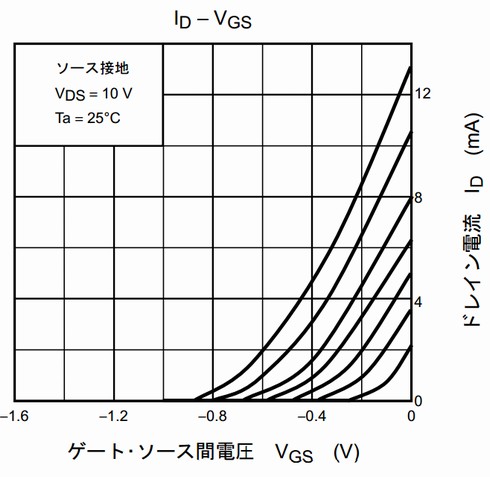

この回路では、JFETであるQ1のドレイン電流IDを使ってオペアンプU1のゲインを調整しているので、JFETの特性ばらつきに注意する必要があります。図3と図4は、東芝のJFET「2SK184」のデータシートに記載されているID対VGS特性です。プロットされた曲線の本数で分かるように、ばらつきがあります。

一般にトランジスタのVBEは、だいたい0.6〜0.7Vと見なして計算できますが、JFETはそういきません。図3の例に示したように、ドレイン飽和電流(IDSS)の個体ごとのばらつきが大きいからです。FET製品は通常、図3中の「注:IDSS分類」に示すように、IDSSの大きさによって「GR」や「Y」、「BL」といったランクに分かれていますが、同一ランクの品種でも個体間のばらつきがありますので、実測することが必要です。

今回の回路では、入力信号がマイナス側に振れて、VGSよりも下振れした場合、JFET内部のダイオードを順方向にバイアスしてしまい、動作しなくなってしまいます。そのため、RFを大きくした方がJFETに加わる電圧を低く抑えられ、入力信号のゲイン可変範囲を広げることができ、かつ、歪特性も良好になります。

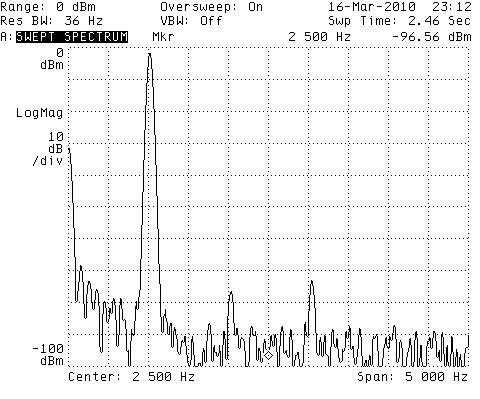

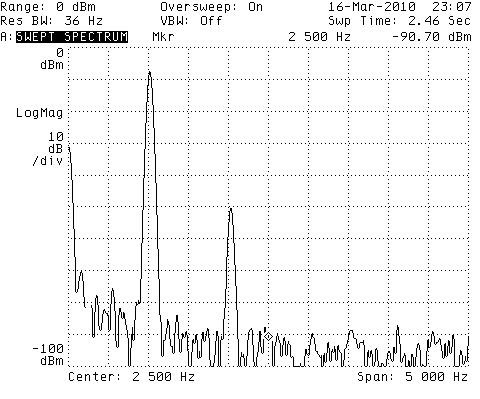

アナログ電子回路技術者に向けた掲示板サイト「アナログ電子回路コミュニティ」のトピックで、東芝のJFET「2SK30A」の歪み特性を計測したデータが投稿されているので、図5と図6に紹介します。図5はVGSが0Vの時、図6はVGSが−3Vの時の歪み特性です。

図5 VGS=0V時の歪み特性 周波数領域の特性をスペクトラムアナライザで観測した結果です。(出典:アナログ電子回路コミュニティのトピック:冬のキャンペーン・スペシャル「AD8302でLCZメータ作ってみましょう!」より)

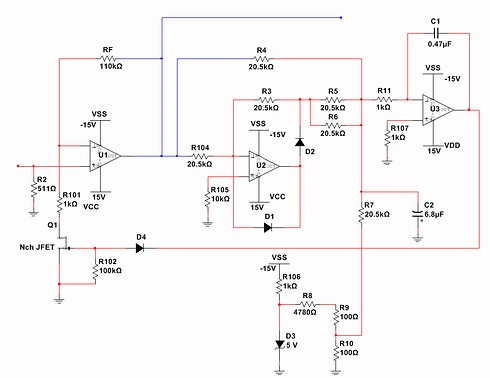

AGC機能を追加する

図7は、このゲイン制御回路を応用してAGC機能を組み込んだ回路の例です(なお、回路図はインターネット経由で入手して無償で利用可能なSPICEシミュレータ「NI Multisim Analog Devices Edition」で作成しています)。

オペアンプを3つ使った回路構成です。簡単に説明しましょう。オペアンプのU1とJFETのQ1は、既に紹介した通りです。オペアンプのU2とU3がAGCの機能を実現するために追加した回路です。

U1の出力は、この回路全体の出力であると同時に、U1自体のゲイン調整のための回路(U2とU3で構成する回路)にも供給されています。U2とU3からなる回路は、U2とコンデンサのC2で絶対値演算を行い、その結果をU3で増幅しています。U3で増幅したその信号を使って、JFETであるQ1を制御する仕組みです。

この回路例では、絶対値演算回路をオペアンプで構成しましたが、代わりにRMS to DC コンバータIC(アナログ・デバイセズの「AD737」など)を用いることもできます。また、信号レベルが大きくなる場合は、歪みを防ぐため、前々回に紹介したソフトクランプを適用することができるでしょう。

関連キーワード

回路 | オペアンプ | トランジスタ | アナログ・デバイセズ | オペアンプ+トランジスタ“ちょい足し”回路集 | シミュレータ | コンデンサ | ダイオード | スペクトラムアナライザ

Copyright © ITmedia, Inc. All Rights Reserved.