解析実行エラーの原因と対策(その4):SPICEの仕組みとその活用設計(9)(1/3 ページ)

第9回では、正帰還回路と初期条件の重要性、および解析エラーを回避する解析手法の選択について説明する。併せて、4回にわたって説明してきた解析実行エラーの原因と対策についても簡単にまとめておこう。

前回は、理想化の問題点やエラーになりにくい解析手法について説明させていただきました。今回は、正帰還回路と初期条件の重要性、および解析エラーを回避する解析手法の選択について説明します。併せて、解析実行エラーの原因と対策が複数回にわたりましたので簡単にまとめておきたいと思います。

正帰還型発振回路が発振しない

正帰還型発振回路とは、特別な発振回路を持たず、回路の潜在的なノイズを選択的に帰還・増幅して回路を発振させるもののことです。発振回路を持たないので、そのままでは発振状態になりません。ですから、正帰還回路を解析するには、動作を理解した上での工夫(=初期設定)が必要になります。パワーエレクトロニクスでよく用いられるリンギングチョークコンバータもこの正帰還回路の範ちゅうに入ります。

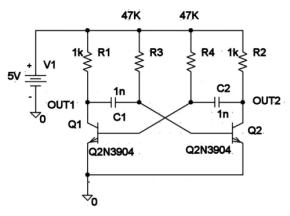

ここでは正帰還回路の代表例として図1に示すマルチバイブレータを取り上げます。

SPICEは初期値やUIC(Use-Initial-Condition:初期条件使用)を指定しないと、キャパシタ開放で回路の初期バイアスを算出します。図1ではQ1、Q2ともに飽和になりますので、このまま安定状態が維持されます。

また、初期値を設定せずにUICのみを指定すると、各素子の初期値を0として計算します。しかし図1の回路では、左右の各部の電位が対称ですから、計算が開始されても状態は対称のまま安定状態が維持されるのが本来の波形なのです。

UIC指定だけで発振させるには、初期解析時間の刻みを非常に短くすることに加えて、動作電源をフェムト(10-15)秒程度で立ち上げるなど、計算有効桁数の限界を越えて非対称成分を生む特別な条件が必要になります。

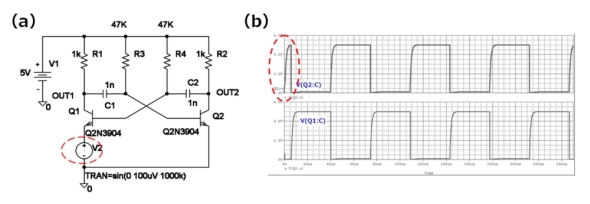

実際の正帰還型発振回路は潜在的なノイズを利用しています。図2(a)では実際と同様に0.1mVのノイズを付加したところ、正常な発振を得ることができました。応答波形の初期(赤丸印)に周期が短いのは、Q2のベース電位が初回のみ−5Vではなく、0Vからスタートするためです。

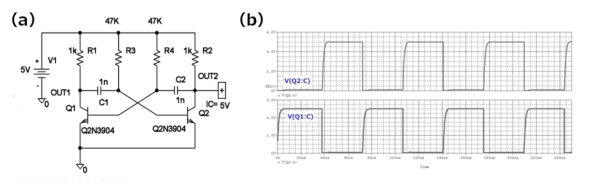

初期条件とUICを指定すると強制的に電位が固定されます。図3(a)ではQ2コレクタが5Vに維持され、この状態から過渡計算が開始されますので、Q2のターンオンに伴いQ1ベースは直ちに−5Vに遷移し、Q1コレクタ(=OUT1)=5V、Q2コレクタ(=OUT2)=0Vで発振を開始します。

注:逆に初期条件を0Vに指定すると、もともとQ2が飽和しているのでQ1をオフさせるのに十分な電圧変化が発生しませんので、発振を開始させることができません。

正帰還回路では、回路の動作を理解していないと正しい初期条件を与ることができないといえるでしょう。

Copyright © ITmedia, Inc. All Rights Reserved.