LVPECLの終端方法――低コスト、低消費電力の“Π型終端”“T型終端”:回路設計(4/4 ページ)

LVPECL(Low-Voltage Positive Emitter-Coupled Logic)の終端方法は、多くの選択肢の中から選ばなければなりません。ですが、選択のための明確な基準は存在しません。本稿では、LVPECLの終端回路の構成と外付け部品の値の決定方法について説明します。

AC結合の終端に対するバイアス

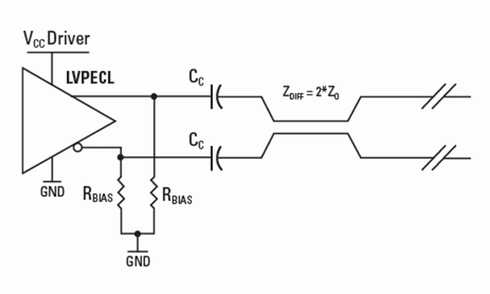

信号の仕様(スイッチングの閾値電圧)が異なるレシーバにLVPECLに対応するドライバを接続する場合には、AC結合を選択することがよくあります。LVPECLに対応したドライバの出力はDC電圧でバイアスされていますが、カップリング・コンデンサを使用してレシーバのコモン・モードの範囲内にバイアスするとともに、伝送路上で終端インピーダンスを与えます。図7に、LVPECL対応ドライバに適用される一般的な回路例を示しました。

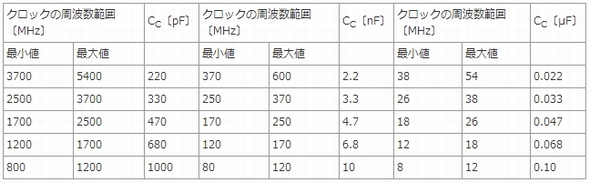

RBIASの値は、表1から得ることができます。この表に示した値は、スイッチングの閾値電圧における出力トランジスタのエミッタ電流に基づいて算出されています。一方、カップリング・コンデンサCCの値はクロック周波数とその周波数におけるインピーダンスの絶対値に基づいて求められます。

CCの値は、それを信号パスに挿入するうえで許容できる寄生リアクタンスの値にも基づいて選択します。表2に、標準的なコンデンサの値とそれに対応する周波数範囲の関係を示しました。この表は、インピーダンスの最大値が0.2Ωであるとして算出したものです。

まとめ

かつての半導体プロセスでは、高性能のp型デバイスを高性能n型デバイスとともに製造することはできませんでした。LVPECLは、そのような時代に生み出された古い技術です。結果として、p型デバイスの機能を実現するために、外付けの受動部品が必要となりました。LVPECLや、その前身であるECLは、この制約を、受動プル・ダウンと伝送路の終端の2つの役割を統合する形で、うまく活用したのです。

設計者は、LVPECLの終端回路の設計に苦労することがよくあります。その理由は、通常は出力段の終端方法について検討する機会がないからです。LVPECLの終端回路を設計する際には、重要な要素である出力トランジスタの電流、部品点数の最少化、消費電力の削減が、終端回路のトポロジや終端用の部品の値にどのように関連するのかを把握しておく必要があります。現在の半導体プロセスでは高性能のp型デバイスを製造することが可能です。結果として、HCSL(High Speed Current Steering Logic)やLVDSのようにグラウンドを基準とする差動信号技術が登場しました。そうした技術では、VTTは完全に不要なものとなっています。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

最大60%の節電効果、IDTのLVDSクロック・ファンアウトバッファIC

最大60%の節電効果、IDTのLVDSクロック・ファンアウトバッファIC

「8P34S」ファミリは、電源電圧を1.8Vに抑えつつ、AC特性は3.3V品と同等の性能を備えたLVDSクロック・ファンアウトバッファICである。精度やビット誤り率などを犠牲にすることなく、最大60%の節電効果と、優れた放熱性を実現できるという。 通信デバイスがなぜか故障、その陰に“活線挿抜”アリ!!

通信デバイスがなぜか故障、その陰に“活線挿抜”アリ!!

RS-485規格のシリアル通信方式は、FA機器の分野に広く普及している。ところが故障品の修理を手掛ける筆者の元には、機器の内部で通信を担うトランシーバICが壊れ、通信不良に陥った機器がたびたび持ち込まれる。調査したところ、電源を入れたまま通信コネクタを抜き差しする“活線挿抜”が、原因を作り出していた。 DDR3がもたらす真のメリット

DDR3がもたらす真のメリット

DDR技術を用いたDRAMは、パソコンやサーバー機器などのメインメモリーとして広く利用されている。現時点では、DDR2が市場の過半を占めているが、次世代に当たるDDR3への移行も進んでいる。本稿では、DDR3のメモリーインターフェース規格の概要を紹介した上で、そのシグナルインテグリティ性能の高さや消費電力の少なさといった特徴から得られるメリットについて解説する。