複雑なSoCでのタイミング収束を短期に済ませる秘訣:設計初期から物理情報を活用せよ(2/2 ページ)

SoC設計は、ますます高度化し、物理的要因を考慮していないSoCアーキテクチャにより、甚大な被害が生じる事態も散見されるようになっています。そこでこれからのSoC設計で重要になるであろう“秘訣”をご紹介します。

タイミング収束とロングパス

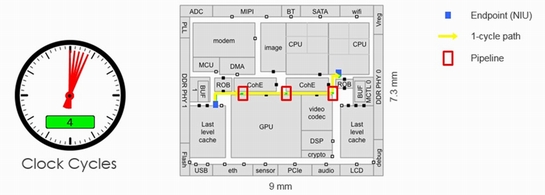

Socインターコネクトにはルールがあり、それは「データが時間内にそこに到達しなくてはならない」というものです。1クロックサイクルでダイ全体に行き渡らせることができたのは遠い昔のことです。つまり伝送遅延があるということは、設計者はタイミングを収束させるためにパイプラインを挿入せざるを得ないということです。チップダイが大きくなるほど周波数が高くなり、プロセスジオメトリが小さくなるほどパイプライン挿入が複雑になります。

例えば、TSMC 28nm HPMプロセスでの比較的適度なサイズの設計を考えてみます。このプロセスで私たちが目標とする動作周波数600Mhzを達成するためには2.2mmごとにパイプラインステージを追加しなくてはなりません。ラストレベルキャッシュとCPUとの間には長い配線があり、この設計には3つのパイプラインを追加する必要があります。

図1 チップのサイズが大きくなるということは、信号が1クロックサイクルで目的地に到達できないことを意味します。設計者は必要なパフォーマンスを達成するためにパイプラインステージを手動で挿入するという手段に頼っていますが、これが設計サイクルの長期化を招いています。フロントエンドのデジタル設計プロセスでバックエンド情報を使用することにより、自動パイプライン挿入でタイミング収束を加速して質を向上させることが可能になります。

より複雑な設計では、パイプラインと無数のパイプラインレジスタを必要とする数えきれないほどのロングパスが存在する可能性があります。タイミング収束と物理的要因を考慮したアーキテクチャに関する問題は、16/14nmプロセスや10nmプロセスではますます深刻になるため、これらのノードではそうした問題を念頭に置いて設計する必要があります。

フロントエンド設計フェーズでの物理検証

Arterisでは、アーキテクチャとRTLでの検証済みインターコネクト情報をレイアウトチームに提供して顧客をサポートしてきました。今では物理的に検証された情報も提供できるため、配置配線が1回で成功する可能性も高まっています。この情報があれば設計者は次のようなことができます。

- 自らのアーキテクチャ上の選択が物理設計に及ぼす影響を見通す。その結果、インターコネクト・トポロジーと輻輳(ふくそう)の観点から配置配線がしやすい、物理的要因を考慮したアーキテクチャを実現できる。

- 設計初期段階でのフロアプランと最終フロアプランをLEF/DEF/TcL形式で読み込む。

- インターコネクトIPと他のIPを物理レベルで分離する。これにより、配置配線ツールがチップ全体でグローバルにインターコネクトIPのみのタイミング収束を実行できる。

- 自動パイプライン挿入によってタイミング収束を加速させ、質を向上させる。大規模設計ではパイプラインを手動で追加していると時間がかかりすぎ、タイミングが実際に収束したことを検証するために配置配線を何度もやり直さなくてはならない。自動化によってタイミング検証済みのインターコネクトをレイアウトチームに提供できる。

- 出来上がった物理トポロジーと関連データを出力し、物理設計プロセスの足掛かりとして使用することができる。16nm、14nm、10nm設計は、配置配線ループの最小化が非常に望ましく、場合によっては不可欠になるほど大規模になると予想される。この物理機能は、顧客が設計の複雑さに対処し、設計コストを抑える一助となる。

設計が複雑になり、製品化期間がますます重要な意味を持つようになるにつれ、エンジニアはそうした課題を克服するいくつかの巧みな方法を思い付くようになりました。アーキテクチャ上のインターコネクト情報をレイアウトチームに提供すれば、複雑さが増すにつれ厳しくなってきたタイミング収束の問題をいくつか回避できます。エンジニアリングチームがこれらの課題を克服するもう1つの方法がコラボレーションです。ここでは私が見てきたエキサイティングな取り組みを紹介しましたので、設計チームがこれらの課題を克服するための他の方法について皆さんからのご意見を伺えれば幸いです。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ユニットレベルのクロックゲーティングで消費電力が下がる! モジュール方式のSoCインターコネクト

ユニットレベルのクロックゲーティングで消費電力が下がる! モジュール方式のSoCインターコネクト

SoCの低消費電力化で見過ごされがちな“インターコネクト”。ここでは、SoCのダイサイズを縮小し、消費電力を低減できるモジュール方式のSoCインターコネクト技術について紹介する。 悪いけど、IPはEDAじゃないよ

悪いけど、IPはEDAじゃないよ

半導体IPビジネスとEDAビジネスを比べている会話を耳にした。彼らは「IPはEDA」だという結論に達した。しかし、いくつかの関連性はあるものの、これらはまったく異なる代物だ。それぞれの分野で10年間を費やした私は、このことを学んだ。 SoC設計で極めて重要なIP品質をどう評価するか

SoC設計で極めて重要なIP品質をどう評価するか

IPの品質は、サードパーティー製IPを使用するSoC設計チームにとても大切です。しかし、新しいIPを使用するときは、どの顧客もある程度のリスクトレードオフがあります。リスクを最小限に抑え、開発期間をできるだけ短縮したいなら、IPを“7つの検証レベル”で評価しなくてはなりません。 理想的なインターコネクト規格を探る

理想的なインターコネクト規格を探る

あらゆるコンピューティングで必要なインターコネクト。オープンな高性能コンピューティングのための「理想的な」効率の高いインターコネクトの特性を紹介する本稿の後編では、規格それぞれの特性を詳しく見ていきながら、理想的なインターコネクト規格を探っていく。