過電流/過電圧保護用のブレーカー回路:Design Ideas アナログ機能回路(1/3 ページ)

今回は、少数の低価格な部品で構成されているが、電流/電圧のいずれかが設定条件を超えると的確に電源を遮断し、過電流/過電圧に対するブレーカーとして機能する回路を紹介する。

過電流/過電圧保護用のブレーカー回路

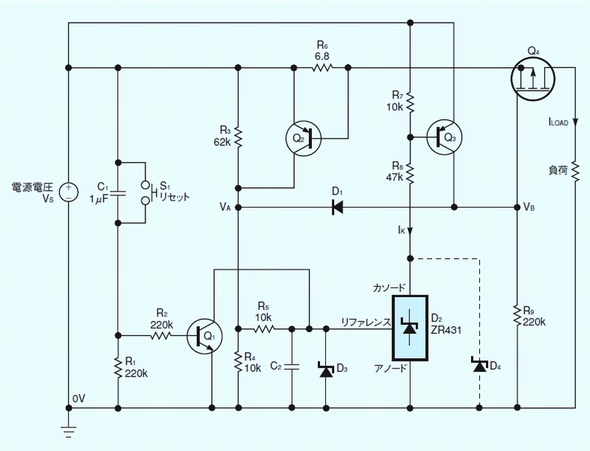

図1の回路は、過電流/過電圧に対するブレーカーとして機能する。少数の低価格な部品で構成されているが、電流/電圧のいずれかが設定条件を超えると的確に電源を遮断する。負荷回路の故障による過電流や、過渡的な高電圧が発生しやすい自動車分野などの用途に適している。

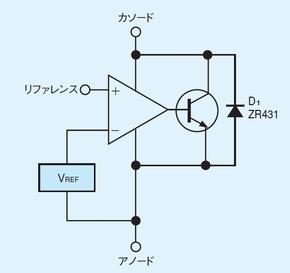

回路の心臓部は、D2のシャント型電圧レギュレーターである。このD2としては、英Zetex製の「ZR431」を使用した。その内部回路を簡略化したものを図2に示す。3端子のパッケージに、基準電圧源とコンパレーター、出力トランジスタを内蔵しており、その動作は以下のようになる。

まず、レファレンス端子(Vref端子)への入力電圧が内部の基準電圧VREF(2.5V)と比較される。例えば、レファレンス端子への入力が0Vの状態では出力トランジスタはオフになり、カソード端子(VZ端子)を流れる電流(以下、カソード電流)は0.1μA以下になる。レファレンス端子への入力がVREFの値に近くなるとカソード電流はわずかに増加する。さらに、入力が高くなり閾(しきい)値である2.5Vを超えると、出力トランジスタが完全にオンの状態になる。その結果、カソード端子の電圧が約2Vに低下する。このときカソード電流は、50μAから100mAの範囲で流せる。

回路の動作を解説

続いて、図1の回路の動作を説明する。まずは過電流保護動作から見ていく。図1の回路において、電源(VS)の挙動に異常がなければ、D2の出力トランジスタはオフの状態にある。そして、pチャンネルMOS FETであるQ4は、抵抗R9を介して印加されるゲート電圧によりオンの状態にある。その結果、電源から抵抗R6を経由して電流ILOADが負荷に供給される。このR6は電流検出抵抗として働き、負荷電流ILOADによるR6での電圧降下(ILOAD×R6)がトランジスタQ2のベース‐エミッタ間電圧VBEとなる。

これにより、ILOADがモニターされることになる。ILOADの値が正常であればVBEは0.6V以下になるので、Q2はオフする。そのため、抵抗R3とR4を接続している点の電圧VAには影響しない。D2のレファレンス端子に流れる電流は0.1μA以下なので、抵抗R5による電圧降下は無視でき、レファレンス端子電圧は図中のVBの電圧とほぼ等しくなる。

Copyright © ITmedia, Inc. All Rights Reserved.