小型化するFPGAがモバイルシステムにもたらす利点:反復アプリケーションの消費電力を抑制

これまでになくインテリジェントとなっている現在のモバイルシステム。新機能が増えることで、システムの電力が大幅に消費される可能性がある。この問題に対処するため、CPUやGPUの代わりにFPGAで細分化された処理を実行することで、システムの機能を最適化する開発者が増加している。

「コンテキスト対応」を提供するモバイルシステム

現代のモバイルシステムは、これまでになくインテリジェントとなっている。ユーザーがより多くの機能を求めているからだ。そのため、設計者の組み込みセンサーリストは増加し続けている。イメージセンサーはジェスチャーや顔認識、視線追跡、動作認識などの機能に対応する。生体センサーは心電図や脳波、体温などを監視する。音響センサーは音声認識、フレーズ検出および位置検出サービスをもたらす。

これらデバイスの多くは「コンテキスト対応」システムを提供し、システムはユーザーに問い合わせることなく、非常に高度なタスク改善の決定を下すことができる。例えば、温度や化学、赤外線および圧力センサーは安全リスクを評価し、危険な環境におけるユーザーの健康状態を追跡可能だ。イメージセンサーと光センサーは、周囲条件が変化しても、イメージの分解能とディスプレイの見やすさを自動的に向上できる。

このような新機能はシステム設計に大きな影響を与える。意思決定を最適化するため、これらのデバイスは可能な限り高速にデータを収集、転送、分析する必要がある。システムの応答速度が高いほど、急速に変化する状況へ正確に適応できるからである。「コンテキスト対応」システムは、環境変化を追跡できるよう常時オンにする必要があるため、新機能が増えることでシステムの電力が大幅に消費される可能性がある。

この問題に対処するため、モバイル向け ヘテロジニアス コンピューティング(Mobile Heterogeneous Computing/以下、MHC)アーキテクチャを取り入れる開発者が増加している。MHCアーキテクチャでは単一のCPUやGPUを使用する代わりに、ASICまたはFPGAを追加して非常に細分化された処理を実行する。

システム設計者がMHCに移行している主な理由の1つは、反復の多いコンピューティングタスクを最も効率の高い処理リソースに任せることで、消費電力を削減できるからだ。例えばGPU、CPUとFPGAの最も大きな違いの1つはそのデータの処理方法となる。

通常、GPUとCPUはシリアル方式で動作し、演算を1つずつ実行していく。設計者がシステム遅延を小さくして、センサー入力へリアルタイムに反応できるようにしたい場合、処理の消費電力を増加させて、システムクロックを高速化する必要がある。FPGAではシステムが演算をパラレル実行できるため、特に処理負荷の高い反復アプリケーションにおいて消費電力が抑制されるといった特長がある。

「FPGAが大型という認識は必ずしも正しくない」

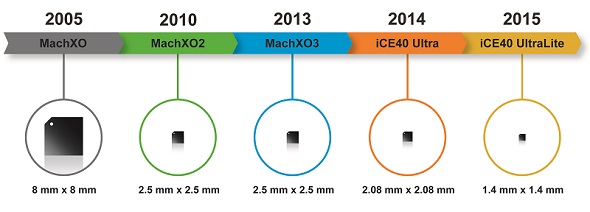

FPGAがこのタスクにあまり使用されてこなかったのは、よくある誤解が原因である。多くの設計者は、FPGAが比較的大型のデバイスだと思っている。これは必ずしも正しくない。わずか1.96mm2と小型なFPGAも存在している。このFPGAが持つI/O数は少なめだが、アプリケーションによっては設計者が必要とする数を満たしている。

例えば、ビームフォーミングアプリケーションで複数のマイクを結合するために必要なI/O数はわずかである。現在では、RFアンテナチューニングやレベルシフトなどの単純な機能用としての1.96mm2サイズから、4Kビデオ伝送に対応した比較的複雑なマシンビジョンアプリケーション用としての6.25mm2サイズまでのFPGAを入手できる。

小型のFPGAは、インテリジェントシステムにも多くのメリットをもたらす。センサーとディスプレイが急増している現代のモバイルデバイスでは、I/Oインタフェースの観点でも新しい課題が生まれている。設計者は、独自またはカスタムソリューションを使用したレガシーシステムなど、センサーおよびディスプレイを多様なインタフェースで集約する必要がある。多くの場合、設計者は小型FPGAやFPGAファブリックを構成するプログラマブルASSPを使用することで、複数のセンサーからのデータを1つのバスに統合したり、複数の異なるインタフェース間をブリッジしたりできる。

I/Oを再プログラム可能なこれらのFPGAは、多様なブリッジ接続やバッファリング、ディスプレイアプリケーションに対応可能だ。最近普及が進んでいるCSI-2やDSIなどの低コストMIPIインタフェースが、この作業に役立っている。

現代の「コンテキスト対応」システムにおいて、データは必需品としての価値を高めつつある。システムは増加し続ける機能リストに対応するため、急速に拡大するセンサーに依存している。しかし、データは素早く効率的に取得し、転送し、分析しない限り役立ない。モバイルコンピューティング市場とMIPIによるI/Oの進歩と、MHCアーキテクチャにおける小型プログラマブルロジックの利点を組み合わせることで、設計者は重要なデータを収集、転送および分析するシステムの機能を最適化できるのだ。

【著者:Abdullah Raouf(Lattice Semiconductor)、編集:EDN Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

FPGAに向けた電源シーケンス回路

FPGAに向けた電源シーケンス回路

システムを設計する場合、電源投入と電源切断のときに発生する、コア電圧(内部回路に供給する電源電圧)とI/O電圧(入出力回路に供給する電源電圧)のタイミングと、その電圧差に注意を払う必要がある。電源投入/切断時に3.3Vの入力電圧を1.8Vのコア電圧に変換し、I/O電圧は3.3Vを保つようにして、2つの電源電圧の差を最小に抑える回路を紹介する。 FPGAの性能を強化する設計ツールの最新版を発表

FPGAの性能を強化する設計ツールの最新版を発表

ラティスセミコンダクターは、FPGA用設計ツール「Lattice Diamond」のバージョン3.7を公開したと発表した。ECP5/MachXO2/MachXO3 FPGAファミリーの性能を強化している。 CCIX技術と広帯域メモリを搭載した16nm FPGA

CCIX技術と広帯域メモリを搭載した16nm FPGA

ザイリンクスは2016年11月、16nm Virtex UltraScale+ FPGAファミリーの新製品を発表した。プロセッサとFPGA間のデータ共有をシームレスにするキャッシュコヒーレントインターコネクト(CCIX)技術と広帯域メモリ(HBM)を搭載している。 コンパイル時間を1/4に短縮する開発ソフトウェア

コンパイル時間を1/4に短縮する開発ソフトウェア

アルテラは、「Quartus Prime開発ソフトウェア v15.1」を発表した。Quartus II開発ソフトウェアをベースとし、Arria 10向けに最適化したSpectra-Qエンジンを統合している。