モデルベースデザイン手法を使ったProgrammable SoCの協調設計【実践編I】:レファレンスモデルからFPGA用サブシステムの作成まで(5/7 ページ)

「モデルベースデザイン手法を使ったProgrammable SoCの協調設計」とはどのようなものか、実践を交えて解説していく本連載。前回の準備編に続き、今回からは実際にMATLAB/Simulinkを用いたモデルベースデザイン手法により実装を行います。

4. FPGA用サブシステム作成

FPGA用モデルでは、HDLコード生成に対応させるため、レファレンスモデルで行っていたようなフレームベースの処理からピクセルデータで構成されるストリーム信号の処理に変更する必要があります。フレームベース処理では、任意のピクセルにランダムにアクセスでき、メモリのハンドリングなどの煩雑な処理をユーザーが記述する必要がないため、使い方は非常に簡単です。

しかし、ハードウェア上で行われるピクセルストリームの処理では、RGB各要素は並列入力されるためそのまま並列で処理を行い、各ピクセルデータはシーケンシャルに入力されるので1ピクセルごとにシーケンシャルに処理を行うことになります。信号処理や制御系では、元々ストリーム信号を取り扱っているため、レファレンスモデルとFPGA用モデルでこのような差はないのですが、画像処理では再モデリングが必要になります。この部分はFPGA用モデル作成のためのピクセルストリーム信号生成と画像処理用ブロックを提供しているVision HDL Toolbox[※記事末のコラム2参照]を使いました。また、レファレンスモデルでは浮動小数点で処理を記述していましたが、FPGA用モデルでは固定小数点化をしています。固定小数点の取り扱いにはFixed-Point Designer[※記事末のコラム3参照]を使用します。

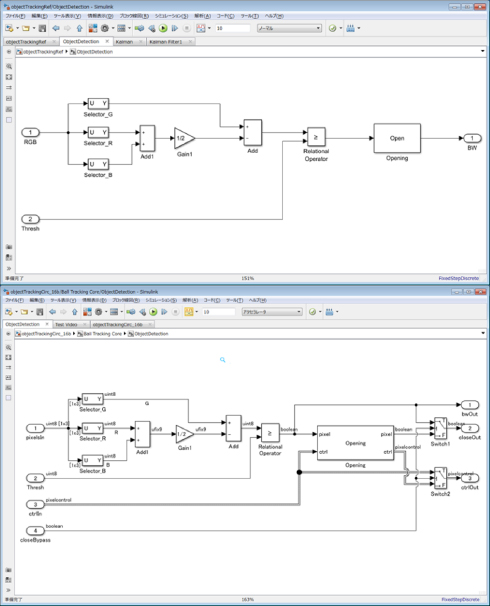

レファレンスモデルとFPGA用モデルを図7に示します。

この部分では一部を同じブロック、一部は同じ機能を持つ別ブロックで置き換えています。具体的には、RGB 3要素のデータをそれぞれに分割するSelectorブロック、加算器、Gain、比較演算は同一ブロックですが、Openingブロックはレファレンスモデルでは、Computer Vision System Toolboxのブロックを使用し、FPGA用モデルではコントロール信号の入出力を持ったVision HDL Toolboxのブロックを使用しています。ブロックパラメーターやアルゴリズムは同一ですので、置き換えるだけでHDLコード生成に対応したモデルに変更できます。

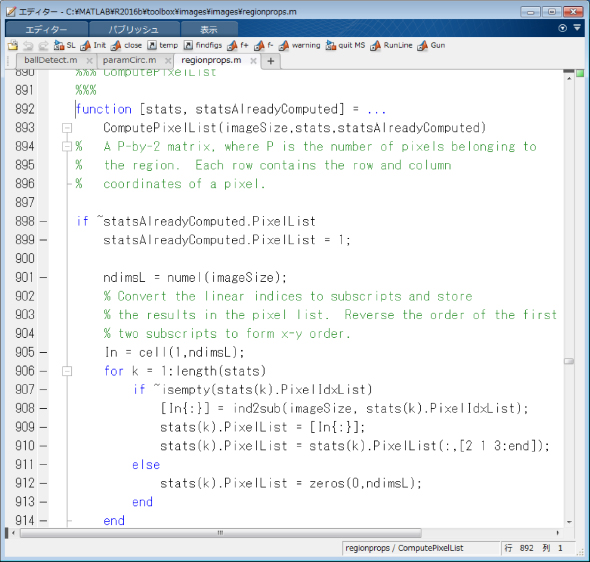

次にregionprops関数またはBlob Analysisブロックで行っていた重心点を計算する処理をFPGA実装用に作り変えていきます。regionprops関数もBlob AnalysisブロックもHDLコード生成に対応していないためです。レファレンスモデルでは、数行のMATLABコードまたはいくつかのSimulinkブロックで記述していましたが、FPGA用モデルでは、カウンター、四則演算などのさまざまなプリミティブなブロックを組み合わせて、コントロール信号を利用して処理を行っています。アルゴリズムがライブラリーとして提供されていれば、それを使用して作成できますが、提供されていない場合は、その処理を抽象度の低いブロックを使って組み立てる必要が出てきます。そのモデルを作る過程では、MATLAB環境であることが役立ちます。多くのMATLAB関数や、一部のSystem Objectで記述されたSimulinkブロックは、そのソースコードが見られるようになっています。ですので、ここではregionprops関数のソースコードを参考にして、モデルを作成していきます。

次のコマンドでソースコードをエディターで開くことができます。

>> edit regionprops

作成したFPGA実装用モデルを図9に示します。このSimulinkモデルでは、まずコントロール信号とカウンターを使って、値が1となっているピクセルのX軸、Y軸方向それぞれの座標位置を算出しています。次に、その座標の積算値をピクセル数で除算して平均化することで重心点を求めています。

Copyright © ITmedia, Inc. All Rights Reserved.