高精度デルタ-シグマADCの 有効ノイズ帯域幅(ENBW)の理解【算出方法】:アナログ設計のきほん【ADCとノイズ】(5)(3/4 ページ)

今回は、「ENBWの算出方法」「システム変更がENBWに与える影響」について、2段フィルターを使用したシンプルな例を説明しながら、デルタ-シグマA/Dコンバーター(ADC)やシステムレベルの設計と絡めて考察していきます。

2つの図を集約して解析

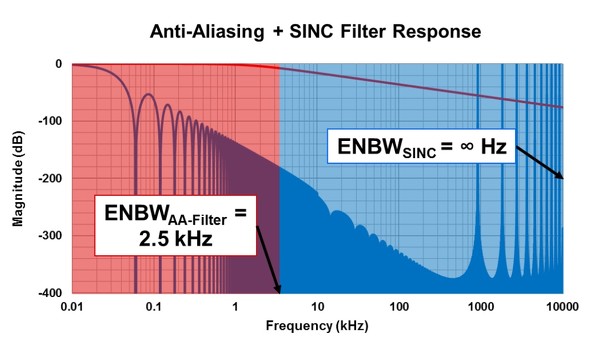

図5は、アンチエイリアスフィルターとSINCフィルター両方の周波数応答のプロット図と、それぞれのENBWを示したものです。

SINCフィルターのENBWが無限大だとすると、この解析をどう続けたらいいのでしょうか。必要なのは、単に積分に制限を設けることです。一般には、変調回路のクロック周波数(fMOD)の数倍(1または2倍)が適当ですが、この例ではアンチエイリアスフィルターを制限として使用できます。

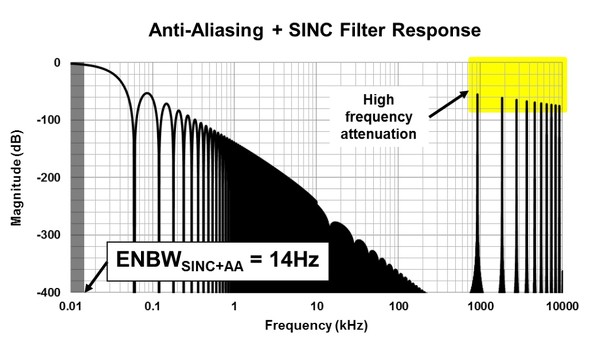

両方のフィルターの振幅(Magnitude)(デシベル単位(dB))が同じX軸目盛りに描画されているので、単純に2つを足し合わせてシステムの全体的なENBWを判断できます。これにより、図6に示すようなフィルター応答が得られます。RCフィルターとデジタルフィルターの応答を組み合わせたものを積分すると、ENBWは14Hzになり、その大きさはそれぞれのフィルター自体より数桁小さくなります。

ENBWが狭くなるのは、高周波数のときのSINCフィルターノイズ電力をアンチエイリアスフィルターが減衰させた結果であり、これによりシステムに伝わるノイズが減少します。このことは、SINCフィルターの無限大の周波数応答を必ずしも考慮する必要がないことを意味します。アンチエイリアスフィルターはすでに、本来なら通過帯域に折り返す、fMODの倍数で発生する高周波数ピークに関連するノイズ電力の多くを除去しています。アナログ設計者の多くは、アンチエイリアスフィルターの所期の目的は低周波数ノイズを除去することだと想定していますが、これは一般にデルタ-シグマADCのデジタルフィルターの役割です。

この想定に従い、カットオフ周波数が非常に低いアンチエイリアスフィルターを設計しようとした場合、一般に抵抗および、容量に大きな値を用いなければならなくなります。しかし、パッシブ部品の値が大きいと信号の静定時間が長くなり、通常は好ましくありません。静定時間が長くなることを許容できたとしても、ADCの入力リーク電流が大きなフィルター抵抗により顕著なオフセット電圧を引き起こすことがあり、システムレベルでの精度低下につながります。従って、パッシブ部品が小さいほど前述の問題を避けやすくなるため、高周波数ノイズに対してだけアンチエイリアスフィルターを設計すればよいということは、実際にシステムにもメリットがあります。

Copyright © ITmedia, Inc. All Rights Reserved.