デルタ-シグマADC使用時における電源ノイズ影響の低減:アナログ設計のきほん【ADCとノイズ】(最終回)(1/4 ページ)

具体的な設計例を用いて、引き続き電源ノイズについて考察します。また、電源ノイズを低く保つベストプラクティスと、システムの総ノイズ特性を改善するデバッグのヒントについても説明します。

前回(第11回)では、電源ノイズについて取り上げ、ノイズが多い電源になる原因や、A/Dコンバーター(ADC)に与える影響などについて述べました。また、ノイズ除去において電源の影響の度合いを測定する方法として、電源除去(PSR)を紹介し、電源ノイズが各種のADC電源に与える影響を分析しました。

最終回となる今回(第12回)は、ADS127L01評価モジュール(EVM)を使用した設計例を用いて、引き続き電源ノイズについて考察します。この設計例を用いることで、システムのPSRを高めようとする際に、どの電源が最も重要かが分かりやすくなります。最後に、電源ノイズを低く保つベストプラクティスと、システムの総ノイズ特性を改善するデバッグのヒントについても説明します。

AVDD、DVDD、LVDD:一番重要なのはどの電源か

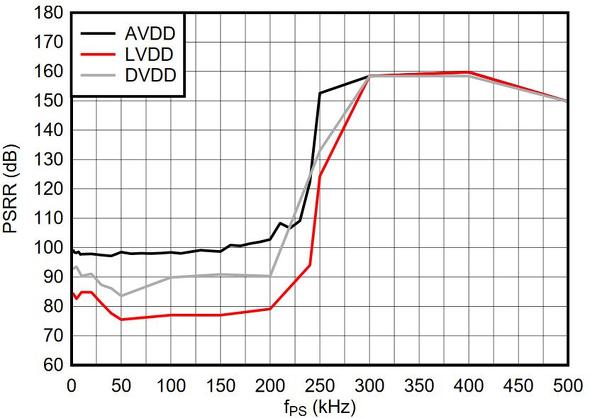

第11回では、「ADS127L01」(Texas Instruments製)で使われる各電源のPSR比(PSRR)を確認しました(図1)。多くのADCと同じように、ADS127L01はアナログ電源(AVDD)とデジタル電源(DVDD)の両方を使用します。説明用にこのデバイスを選んだ理由は、このデバイスには低電圧ドロップアウト電源(LVDD)と呼ばれる3つ目の電源が必要だからです。LVDDは、ADS127L01のデルタ-シグマ変調回路に直接電源を供給します。LVDD電源は、内蔵低ドロップアウト(LDO)レギュレーター(AVDDに接続)または外部LVDD電源のどちらかから供給されます。この記事の後の方で述べますが、ノイズの多い電源を使って外部からLVDDを駆動すると、ADCのノイズ特性への悪影響が最も大きくなります。

図1を見ると、3つの電源のうちでLVDDのPSRRが最も低いため、ADC出力への結合ノイズに最も影響を受けやすいのはLVDDになります。LVDDはデルタ-シグマ変調回路に直接電源を供給し、次に変調回路がアナログ入力からデジタル出力への変換処理を直接制御するため、LVDDがノイズの影響を最も受けます。それに比べてAVDDは、メインのバイアス電流の生成を含め、その他のアナログ回路に電源を供給しますが、変換処理の結果に与える直接的な影響は大きくありません。ADCのデジタルコアに電源を供給するDVDDは、変調回路の出力がデジタルデシメーションフィルターに達する前にすでにバイナリ形式になっているため、変換処理の結果に与える影響は最も低くなります。複数の電源が必要なデバイスでは、デルタ-シグマ変調回路に最も直接的に電源を供給する電源を優先させますが、通常はAVDDです。

ノイズの多い電源で変調回路を駆動したときの影響を実物で明らかにするために、ADS127L01評価モジュール(EVM)で入力短絡によるADCのノイズ測定を行いました。使用した条件は次の4つです。

- AVDD、LVDD、DVDDにクリーンな電源を供給(リップルなし)

- AVDD=3V+1kHz、100mVPリップル、クリーンなLVDDとDVDD

- LVDD=1.825V+1kHz、100mVPリップル、クリーンなAVDDとDVDD

- DVDD=1.8V+1kHz、100mVPリップル、クリーンなAVDDとLVDD

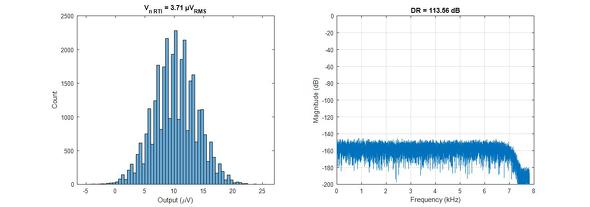

それぞれのケースで、ADCの入力同士を短絡し、それに中間電源電圧(1.5V)のバイアスをかけ、ADCのフルスケールに対する実現可能な最大の信号対雑音比を計算しました。この結果は、ADCのダイナミックレンジと呼ばれます。ADS127L01データシートの表1に、ADCの動作モードとデータレートのそれぞれに対する標準ノイズ特性が記載されています。このテストは、オーバーサンプリング比を256にし、広帯域2デジタルフィルターを使った4MHzクロック入力の超低電力モードで行われました。表1から、この設定のときのダイナミックレンジは約114dBと想定されます。

想定通り、EVMは、ADC電源ピンの3本すべてにクリーンな電源を使用したときに最も高い性能を発揮します。図2は、この条件でのノイズヒストグラム(図左)と高速フーリエ変換(FFT)(図右)のグラフです。ダイナミックレンジは113.56dBと、データシート仕様に非常に近くなっています。

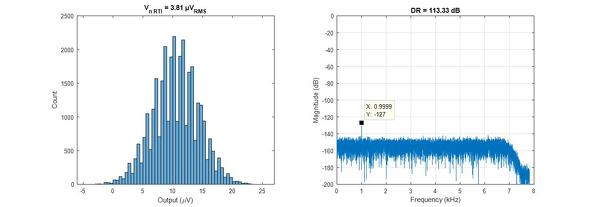

次に、3VのAVDD電源に1kHz、100mVPの正弦波を乗せました。この正弦波は電源ノイズを模しており、公称AVDD電源電圧(3V)と等しいDCオフセットで信号発生器を使ってADCに与えます。このケースでは、このノイズはADS127L01の内蔵LDOでもほとんど除去することができ、図3に示すように113.33dBの定格性能を維持できました。1kHzの周波数スペクトルに−127dBの大きさのわずかなトーンが現れているのが見えるでしょうか。これは、フルスケールに対する元々の入力信号レベル(2.5VのADCリファレンス電圧に対して−28dB)からAVDDのPSRR、つまり約100dBを引いたものと相関があると思われます。

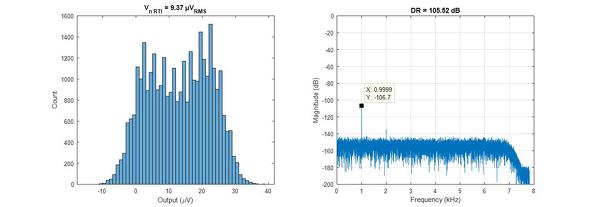

次のテストでは、EVMのAVDD電源をデフォルトに戻し、信号発生器を使ってLVDD電源を供給します。このテストでは、1.825VのDCオフセットを中心とする1kHz、100mVPの正弦波リップルを入力し、内蔵LDOはバイパスしています。その結果、LVDD電源ノイズが原因で、図4に示すようにノイズ特性が大きく悪化しました(105.52dB)。また、図3の右図に比べて、周波数スペクトルの1kHzのトーンがよりはっきりと見えます(−106dB)。

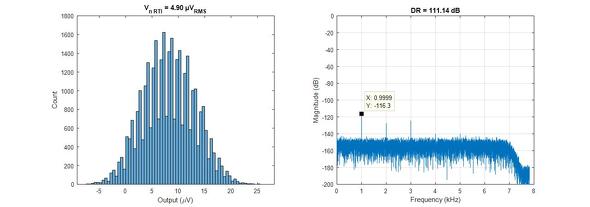

最後のテストでは、EVMのAVDDとLVDDをデフォルトのクリーンな電源に戻し、DVDDに正弦波を与えました。このケースでは、1kHz、100mVPの正弦波リップルの中心は1.8VのDCオフセットです。興味深いことに、図5では、FFTでは1kHzリップルの高調波成分が増えているにもかかわらず、ダイナミックレンジはLVDDで試したときよりも悪化していません(111.14dB)。

最終的に、これらの実験からは、図1の結果が確かめられるとともに、一部の電源(特にデルタ-シグマ変調回路に供給する電源)は他の電源に比べて電源ノイズの影響を受けやすいということと、そのため高いPSRを維持するにはこれらの電源に特に注意する必要があることが再認識できます。

Copyright © ITmedia, Inc. All Rights Reserved.