ステップダウン形DC/DCコンバーターの設計(2):たった2つの式で始めるDC/DCコンバーターの設計(4)(2/4 ページ)

今回は前回の検討で得られた各部の波形からスイッチング動作に関係する素子に要求される特性項目と値について説明します。

各部品の要求特性

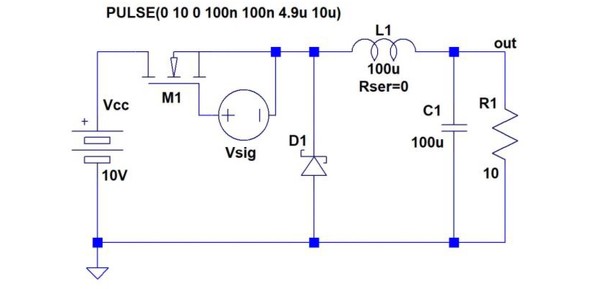

ここでは理想化された回路図ではなく、実際の回路に近い図2や前述の図1を元に各部品の要求特性について考えます。

FET(M1)

FET-SWオフ時には回路説明で述べたように次の現象が発生します。

「このようにオン時とオフ時では電流の流れの一部が切り替わります。この電流の切り替わりや前述したチョークLの誘起電圧の反転が後で述べるDC/DCコンバーターのノイズ発生の源になります」

この電流の流れが急に切り替わることに起因して各電流経路の浮遊インダクタンスLeを原因とするLの式(E=L×ΔI/Δt)によるスパイク電圧がLeに発生します。

FETがオン、オフして回路電圧が急変すれば回路につながっている部品の寄生容量への充放電電流がCの式(I=C×ΔV/Δt)に従ってヒゲ状の電流になって流れます。特に図3に示すようにFETのターンオン時に流れる電流をターンオンピーク電流IdMとします。

このスパイク電圧やIdMを計算することは計算精度の点からあまり行われず、実際の設計では経験則による次のような補正が主に用いられています。

VDSS:FETのドレイン-ソース間の最大定格電圧です。M1がターンオフするとFETのドレイン(D)は電源電圧Vに、ソース(S)はD1の−VFの電位になります。したがってFETのD-S間には(V+VF)の電圧が印加されますがこの値は理論値です。実際には各素子やパターンの寄生成分によってスパイク(リンギング)電圧が20%程度上乗せされて印加されますのでFETのVDSSはこの上乗せ値に対してマージンを取らなければなりません。ディレーティングを80%とすれば1.2/0.8=1.5倍の値を考えればよいでしょう。

Id(DC):FETのドレイン定格電流Id(DC)です。

ドレイン電流の各部の波形の名称は図3に示す値とします。

M1のドレインに流れる電流Idは既に説明したように、“(チョークLの変動分ΔI)/2+出力電流Io”がオン期間tONに流れます。この値がIdPです。

ただし、この値は理論値であり、実際のFETのターンオン時に前述のヒゲ状のターンオンピーク電流IdMが重畳されますのでその分を考慮しなければなりませんが幸いなことにFETのドレイン電流定格にはパルス定格Id(Pulse)が定義、保証されています。

一般にId(Pulse)=Id(DC)×(2ないし4)であり、また実際の時間幅もヒゲ状のため温度上昇には寄与しないのでIdMについては特に熱的には考慮しなくても問題はなく、測定値IdMはId(Pulse)の80%に収まっていれば問題ありません。したがって必要な電流定格の値は次の3式、4式の値とします。

RON:FETのオン抵抗RONです。

FETはオン時に抵抗性の物性を示します。FET(M1)がオンしている時、ドレインには次のようなジュール損が発生します。このジュール損に関係するのがFETのオン抵抗RONです。

ここでV(OUT)は出力電圧ですが実際にチョークに印加される電圧はFET(M1)の電圧降下(≅Io×RON)を見込まなければなりませんがRONはまだ決まっていません。

ここでは経験的にこの電圧降下がダイオードD1のVFに等しいと仮定して通電率δを補正します。したがって実際のドレイン損失PDは5式になります。この式でVは動作電圧です。

このままFETの最大許容損失PD(MAX)以内だからといって設計を進めるとPD(MAX)は温度上昇125℃を前提としていますので実機で高い温度上昇を示してしまいます。ですから実際の許容損失はこの温度上昇を考慮しなければなりません。FETに許される温度上昇ΔTchは前述の通り40℃までです。

ただし、FETのオン抵抗には高温時(Tch=150℃)、25℃の値のおよそ2倍になる温度特性がありますので25℃の時のRONはこの値の50%以下にする必要があります。

したがって

が1つの条件になります。逆算すると必要なオン抵抗RONは7式以下の値が要求されます。

[計算例]

1つの例として24V入力、5V出力、Io=5A、D1のVF=0.5V、Rth(H)=30℃/W、Rth(J-C)=3.125℃/W*とすると、必要なRONはどの程度のFETを選ぶべきか?

7式に従って計算すると

となります。最大許容損失PD(MAX)が40Wのパッケージ品ならId(DC)=20AぐらいのFETになります。IoやIdPだけから計算するとId(DC)は7〜8Aのものでも十分ですが温度定格を考えるとこの例ではRONの制限の方が厳しくなります。

ここで通電率δを計算すると5.5/23.5=0.234、高温時のドレイン損失PDはPD=52×(0.1×2)×0.234=1.17W、温度上昇ΔTchはΔTch=1.17×(3.125+30)=39℃となりました。

M1導通時の電圧降下を計算すると高温時は2×0.103×5=1.0Vとなり予想より電圧降下が大きくなりますがRON=0.103としてδを再計算しましたが結果に大差は生じず、また温度上昇ΔTchも想定内ですからこのままとします。

*ΔTch=125℃、PD=40WのFETではRth(J-C)=125/40=3.125℃/Wです。

またFETの場合はチャネル損失ですから添え字はchですが接合部の意味でjも使います。

Copyright © ITmedia, Inc. All Rights Reserved.